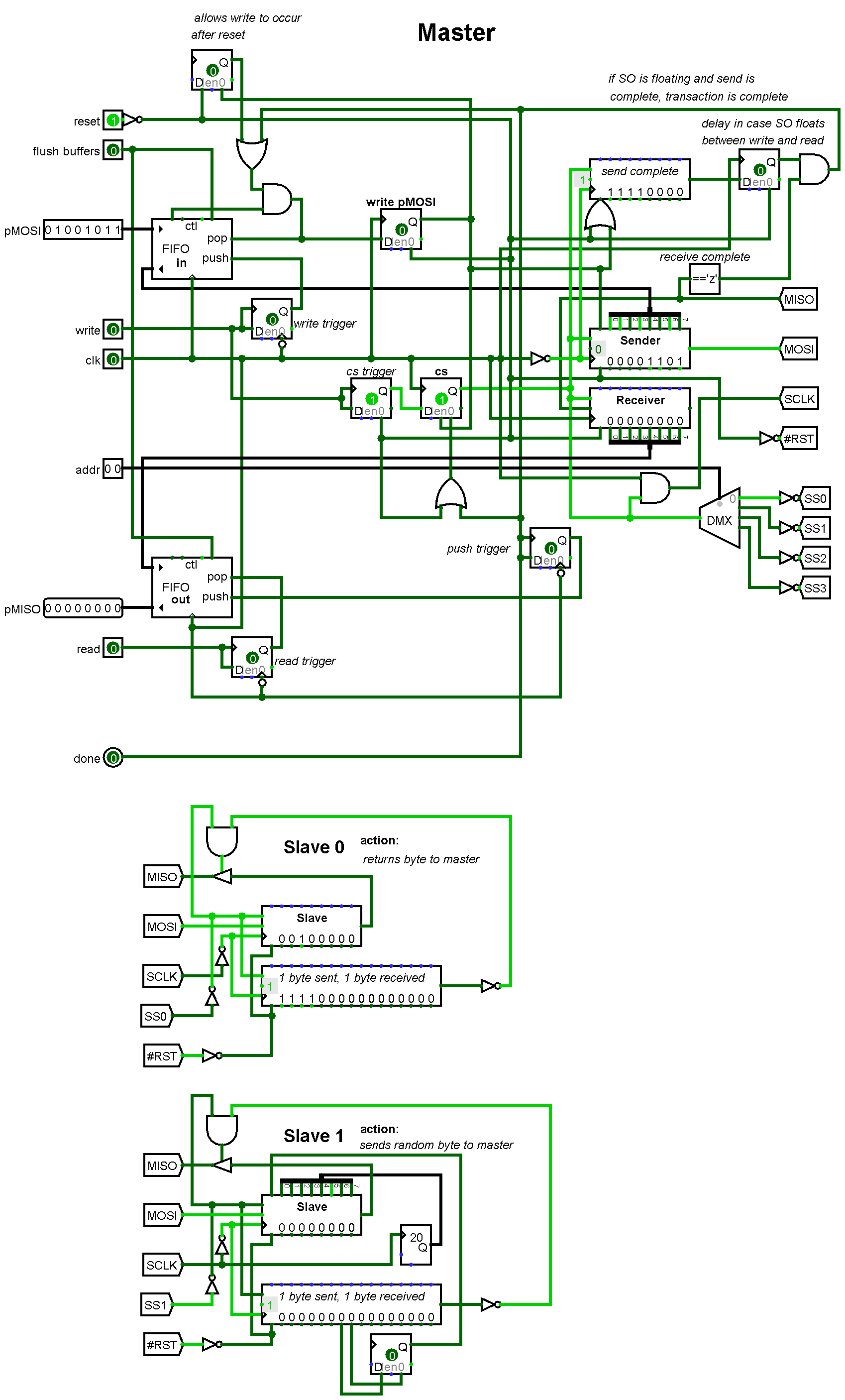

This controller adds more functionality that the other lacked. The operation of the controller itself is almost entirely standalone and only requires an input of a clock signal and a steady address signal during operation. I added a FIFO to the input as well so that the data in the shift register is not overwritten when the write input pin is asserted. In addition, a D-FF is set whenever the write pin is asserted, and the flip-flop is only reset when the master has sent a byte and the slave is no longer sending data (might need changing depending on operation of slaves). The output of the D-FF is the cs signal, which is inverted for the ~cs line to the slave. Currently there are only two slaves; one sends the byte it receives back to the master, and the other sends a pseudorandom byte to the master. Here's the .circ file on Github.

SPI controller

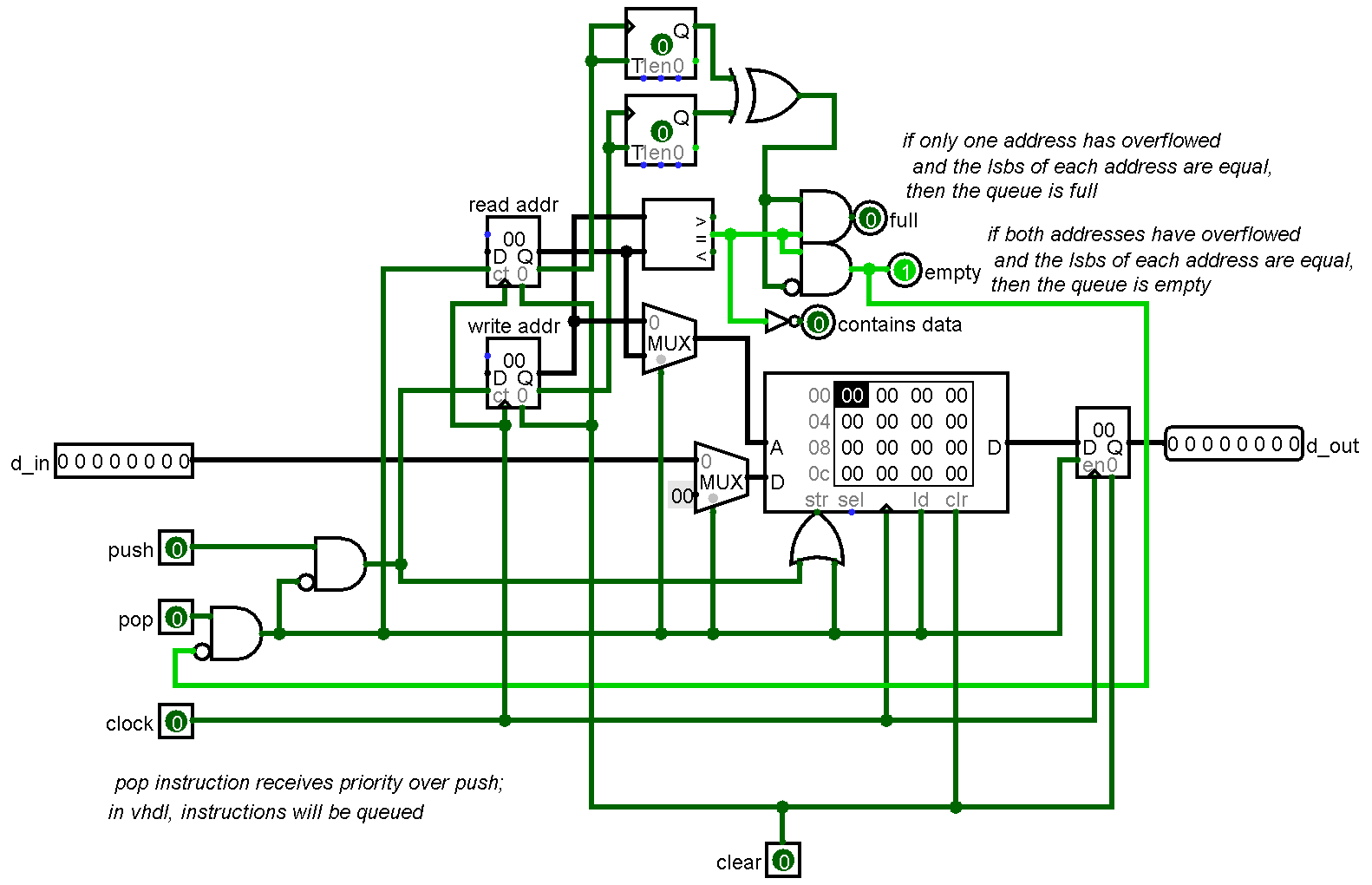

Updated FIFO:

Reed Foster

Reed Foster

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.