This is the contents of the Project Details page but it was getting too long so I moved it here ;-)

External references

I wouldn't jump head-first like that without some good resources that encourage and feed my curiosity ;-)

Of course I heard about Zuse's computer but my first exposure was when I was part of the Homebuild CPUs webring and I encountered projects such as Harry Porter's or TIM-8.

Some naughty dutch guy woke the devil with his #Relay Logic Clock and I should give it even more attention...

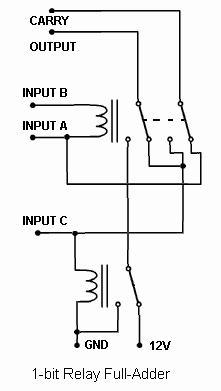

But the last trigger was Basic Relay Computer where you can find such enlightening drawins as the following:

This means: one SPDT and one DPDT, or three SPDT. My idea becomes possible.

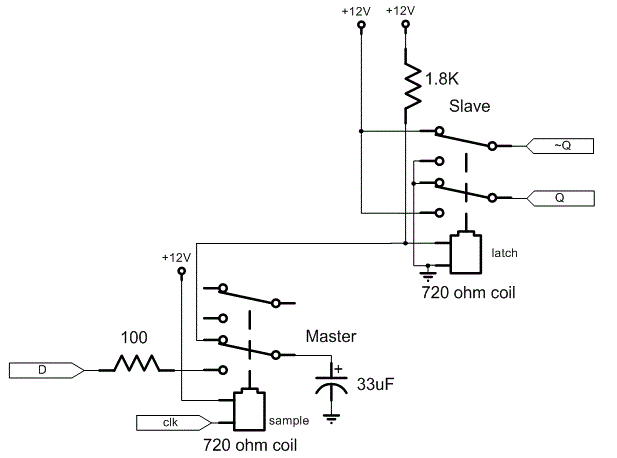

Then the last straw is the storage, explained at http://relaysbc.sourceforge.net/circuits.html

It becomes possible to design a circuit with a low relay count. However a mix of SPDT and DPDT seems desirable, less coils,less noise, less power consumption !

Here is a rough analysis of the parts cost of a 16-bits computation unit:

Addition

This is pretty easy and uses about 3 SPDT.

Multiplied by 16 bits: 48×SPDT.

Subtraction

Again, easy : XOR the subtractand and set the carry input.

XOR is one SPDT, plus a big switch to select the function, so that's 16 SPDT.

Multiply

The above was pretty easy but there are some relays left in my virtual budget. Multi-cycle multiplication is possible by reusing the adder, and with the help of a rotating register.

Division

If you figured out the multiplication, the division is almost as easy, but by iterating subtractions and rotations, instead of additions.

Registers

Using the capacitor trick, it's possible to implement a DFF with 2 SPDT and a capacitor. However the source data must be chosen (input dials or adder's result) so that's 3 SPDT. Division requires an additional mux to select the shifted register or the Adder's output, in case the carry/borrow is set... 4 SPDT, 128 relays. I should refresh my memories about restoring and non-restoring division, I think...

Update (20160501): No MUX2 ! see A sick trick for the multiplies. This saves at least 16 relays (I might extend the ALU to 20 digits then) and the accumulator would be loaded through the adder (by clearing the mulpliplicand before addition).

I should also check HOW it is possible to compute a 32-bits number with only a 16-bits adder. The 8086 did it this way, 35 years after Von Neuman described how to do it, but I forgot the details...

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.