Hello again :-)

Apologies for my late reply. Winter can be a challenging season for those with inept immune systems.. :-(

While I overcame my health hurdles, in my last blog update you may recall I was to make attempt at building Ohm pre-production boards? Well, turns out the PCBs that I had received were indeed of an inferior quality :-( So I am now in the process of moving my Ohm board design to another PCB house..

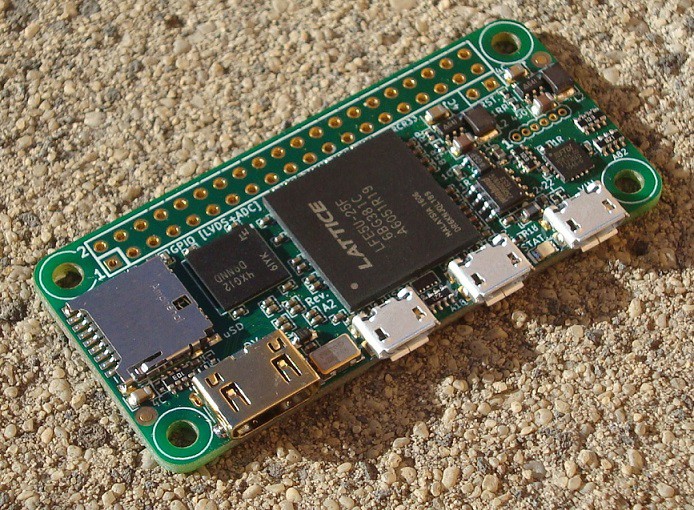

Now, while that was all going on, another major thing happened.. I basically had another crack at building a pi zero sized FPGA devboard again. Here's the result - (re)introducing my 'Flea Ohm' board! :-)

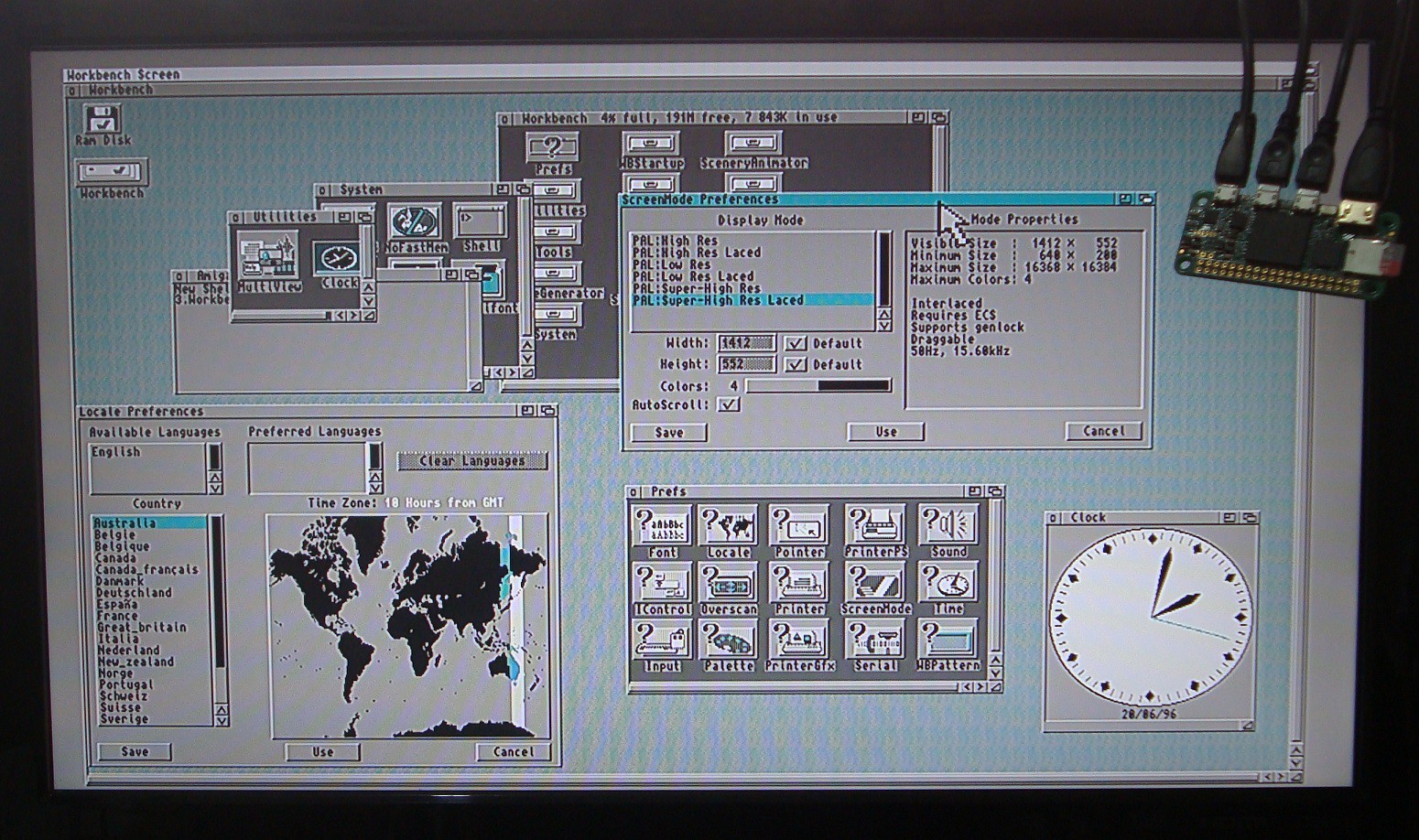

.. and here it is running a test configuration in the shape of the Minimig core:

So.. now it looks as though I now have two possible designs to explore further (ie. Ohm and as-yet-unnamed Ethernet variant :-) Time permitting, I hope to do a small run of one or both boards (depending on interest) in the near future.

Thanks for reading! More to follow..

Valentin.

Valentin Angelovski

Valentin Angelovski

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Hi Valentin,

Wondering how many layers these boards are and what is the trace/space sizing

Cheers - mark

Are you sure? yes | no

Hello Mark,

I use four layers (and attempt to optimize the heck out of them as one does :-) on my current creations but I am toying with the possibility of going to six or eight layers. Also, I alternate (depending on the board) between 3/3 and 4/4 mil. track/space. Cheers.

Are you sure? yes | no

Wow, the Flea-zero board looks really sweet! Quite the squeeze you put on that FPGA, I am sure it must have been a joy to route. :-)

Are you sure? yes | no

Hey Xark, long time no chat :)

Thanks. You're right, redesign of my board using the larger ECP5 FPGA package style very nearly didn't make the final cut..

Cheers, Valentin.

Are you sure? yes | no

Hi Valentin,

I'm really happy to see this zero ohm board back again. What kind of memory did you put ?

When can we hope to see those board available ?

Thanks for this excellent work.

Are you sure? yes | no

Hello! Thanks, I'm glad it came back too :-) To keep things simple and low-cost (not to mention compatible with existing HDL examples), I decided to stick with SDRAM. On the prototype pictured in the blog I have a 32MByte DRAM installed. I have made some other improvements to the Ohm board i.e. like 12 LVDS lanes broken out instead of only eight at the GPIO as well as a more familiar connector layout..

In the longer term, I may try for a DDR RAM variant - if I ever figure out how I can make it all fit on the PCB that is (thanks to the relatively huge FPGA package compared with before..).

I have successfully tested the new prototype pictured above and so I can now move towards a small production run of boards. With luck, this could begin as soon as late next month. More details to follow..

Cheers, Valentin.

PS: On my larger Ethernet-enabled board (of which I am thinking of calling the "Giga"), I went for 128MBytes of low-voltage SDRAM.

Are you sure? yes | no