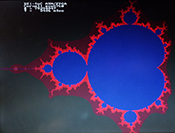

-- Mandelbrot set on VGA/HPS

This example is a base-line implementation of a mandelbrot solver

which displays using the DE1-SoC computer system explained below. It

computes a 640x480 approximation with a maximum of 1000 interactions in

about 3.4 seconds, using level -O2 compiler optimization. The code

computes about 23 million complex iterations/sec (40 cycles/iteration).

The colors are approximately logarithmic in number of iterations at that

point. Image.

The total number of iterations for all points on the screen and total

execution time are displayed. Also included is a routine to erase all

text on the screen.

The game of life is a 2D, totalistic, cellular automaton which is compute-universal. The HPS program displays using the DE1-SoC computer system explained below. It computes a 640x480 cell automaton at approximately 14 frames/sec, using level -O2 compiler optimization. This corresponds to about 4.25 million cell updates/sec. The slow step here is writing the pixels to the frame buffer, which is limited by the bus rate to about 5 million/sec. If you modify the code to be smarter about writing pixels, the speed goes as high as 60 frames/sec, or about 18 million cells/sec, but will depend on the specific content of the screen. More cell state changes will slow down execution.

The game of life is a 2D, totalistic, cellular automaton which is compute-universal. The HPS program displays using the DE1-SoC computer system explained below. It computes a 640x480 cell automaton at approximately 14 frames/sec, using level -O2 compiler optimization. This corresponds to about 4.25 million cell updates/sec. The slow step here is writing the pixels to the frame buffer, which is limited by the bus rate to about 5 million/sec. If you modify the code to be smarter about writing pixels, the speed goes as high as 60 frames/sec, or about 18 million cells/sec, but will depend on the specific content of the screen. More cell state changes will slow down execution.

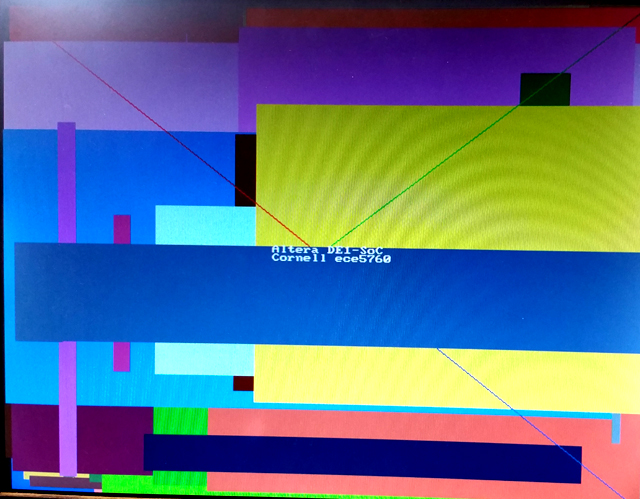

--The DE1-SoC_Computer hardware

The directions written by Shiva Rajagopal for Qsys 640x480 converstion worked for this system. (system ZIP) The span of the addresses in the virtual-to-real memory map had to be doubled. and, of course, the addressing and colors of pixels had to be modified in the main program.

The size of the character buffer was not changed. The color encoding is

now 8-bit with top 3 bits red, next 3 green, lower 2 bits blue.

VGA_line(0, 0, 320, 240, 0xe0) ; // red 3-bits

VGA_line(639, 0, 320, 240, 0x1c) ; // green 3-bits

VGA_line(639, 479, 320, 240, 0x03) ; // blue 2-bits

The design was very slow to generate (Qsys) and compile (Quartus). It

took around an hour (on my 5 year old machine). Next step is to speed it

up. Chopping out the Nios CPUs and some of the support, but leaving the

video in/out and audio reduces the generate time to 5 minutes and the

compile time to about 22 minutes. (archive).

Stripping out the rest of the LED and switch i/o and removing the

video-input funciton reduces the compile time to 18 minutes.

A better chopped down system keeps the LEDs, switches, 640x480 video out, and audio. The design is partitioned so that the DE1-SoC computer is in its own partition. Two other partitions are top and the hex display modules. On my new computer (4 core, 32 GB memory, SSD, July 2016), this takes 12 minutes for a full compile. A small change to the hex display partition takes about 8.5 minutes to recompile. A small C code tests the hex display partition. (C code, address header, project ZIP).

Bruce Land

Bruce Land

Erik Piehl

Erik Piehl

Nicola Wrachien

Nicola Wrachien