Still reading Dieter Müller's articles...

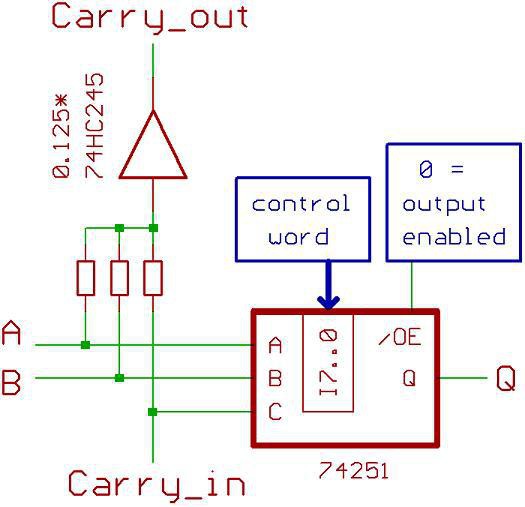

The idea of the majority gate designed with parallel resistors (or a crude DAC ?) is too tempting and I understand his fascination. Looking at this diagram:

This could be translated into ECL or resistor-relay logic almost directly !

Now the question is: could this work with my pre-biased logic cell and what is the value of the parallel resistors ?

20160925: Hysteresis would kill the design but all hope is not lost. Switching from a "DAC" to a "current adder" could be a solution. Diodes let the current go through one direction and this is great because the relay is mostly a current-driven device.

However, according to this log, the coil current must be >= 60mA to turn the relay on, and less than 25mA to turn it back off. The Hysteresis is way too high to make the current adder useful. Is there a way to reduce a relay's hysteresis ?

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.