SDR With FPGA is soo cool:

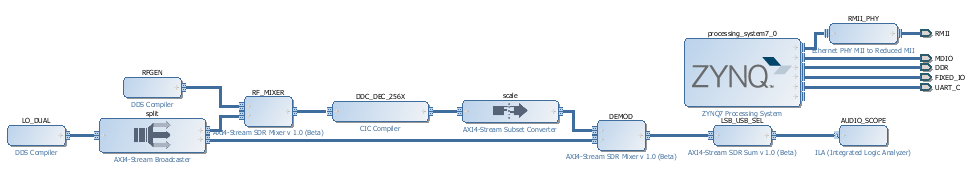

Most of the blocks are just there for you, I had to create only two very simple blocks to complete the SDR. First I made a SDR Mixer designed to work with multichannel AXI4 Streams. To optimize resources the LO is made also multichannel, so the same DDS generates the actual LO sin/cos and also the sin/cos for the weaver demodulator, this saves many BRAM's. My SDR mixer takes either RF input or I/Q input and mixes (that is multiplies) it with the LO signal fetched from the multichannel LO stream. This IP Core is basically just one DSP48. The other IP Block I made also works on multichannel stream and uses one DSP48 to add the incoming interleaved data samples. So it will select either LSB or USB to be demodulated.

For proof of concept I added signal generator to mimic the received Transmitter signal into the FPGA so that I do not need any external signals for initial debug.

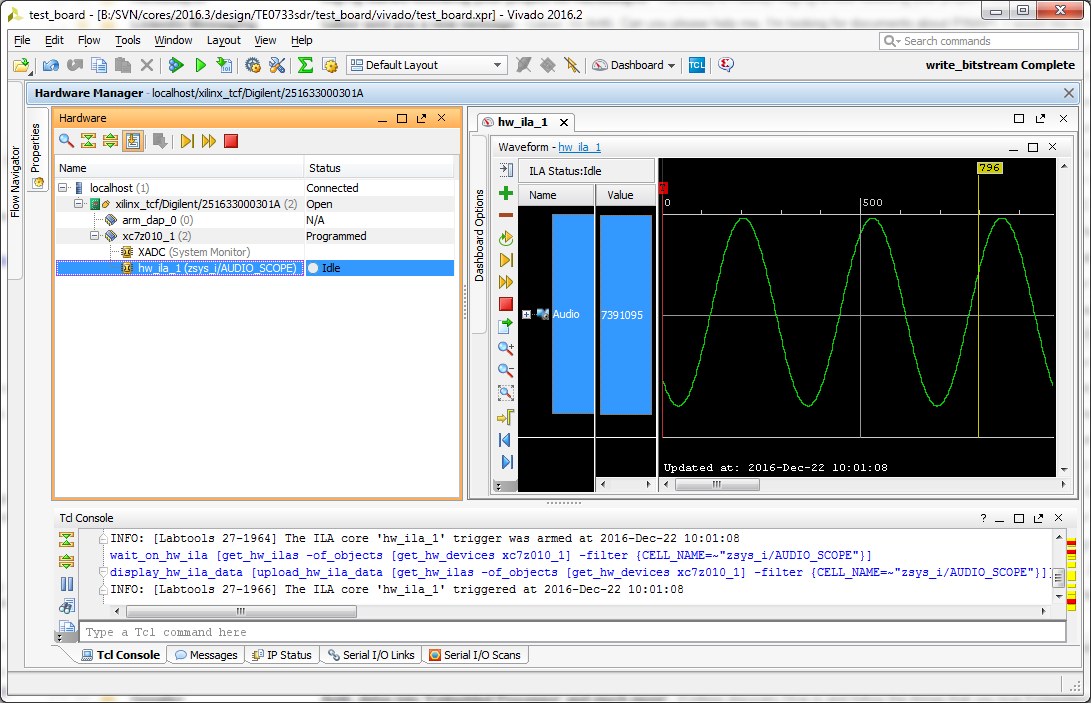

And here it is the demodulated CW audio signal after weaver demodulator.

RF input is set to 3.5MHz

LO is set 3.5003MHz,

Weaver LO is set to 300Hz

and demodulated CW audio is then 600Hz tone! Working!

This is proof of concept mainly, there are several filters still missing in the design, but those are just click and configure to be created, they will also be implemented as multichannel to process both I and Q samples in the same FIR filter.

All the receiver will easily fit into Zynq 7010, actually several such channels will fit also.

Antti Lukats

Antti Lukats

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.