Building a computer from scratch

To make the experience fit your profile, pick a username and tell us what interests you.

We found and based on your interests.

epRISCv4_defs.vDefinitions for the corex-verilog - 544.00 bytes - 10/06/2016 at 14:35 |

|

|

epRISCv4_core.vCPUx-verilog - 16.57 kB - 10/06/2016 at 14:35 |

|

|

epRISCv4_gpr.vRegisters for the corex-verilog - 1.09 kB - 10/06/2016 at 14:35 |

|

|

lemon_v4.asmSimple monitor program - assemblyasm - 9.74 kB - 10/06/2016 at 14:35 |

|

|

epRISC_v4ISA specificationeprisc_v4 - 11.97 kB - 10/06/2016 at 14:34 |

|

I don't have as much time to work on this project anymore, but I still pick it up for a few weeks at a time every now and then.

There's an emulator available for the epRISC board now. It's written in plain C++ and supports the barest minimum of peripherals to be useful (the UART). Verilator is used to emulate the system directly from the Verilog source, so anything that runs on the emulator should run on the real thing.

On the software side, I'm starting to replace the old disk format with ext2. There's nothing cool to do with it yet but I have it parsing MBR entries and superblocks.

So it's been almost five months since the last update.

In that time, I've spent an unreasonable amount of time, money, and sleep on getting the computer to work. And work it does - although it's brittle, the system can start itself up, check its memory, load an executable of the user's choice from an SD card (with a basic filesystem), and run it from the SDRAM, all without a hiccup.

Working on the system deteriorated my grades to the point that I almost didn't graduate. All but one of the colleges I applied to didn't even bother to look at it. The final presentation, which was supposed to be a 30-minute presentation to a panel of engineers, was eventually reduced (due to circumstances outside of anyone's control) to a 12-minute show-and-tell to my classmates, who were largely kept in the loop with the project's progress anyway.

I'm not convinced it was worth it.

I'm tired. This project has drained me mentally, and the realization that I spent so much effort for virtually no payoff keeps me up at night. I'm not ready to continue working on this project, not for a long while.

Over the next few weeks, I'll be posting regular updates on this page, a postmortem of the good, bad, and ugly of the past eight months. With any luck, at some point I'll be able to return and continue, and maybe the lessons I've learned can help one of you on your own projects.

Just a quick post of this week's changes:

The CPU's interrupt module is implemented and (should be) working. My plan is to replace it at some point with a more advanced system, but for now the simple version is fine.

I've started writing the assembly specification document. It defines the format for epRISC assembly files, as well as assembler directives and the full instruction set.

I've also started defining the sysX (SYStem eXpansion) protocol. It's essentially just Quad SPI with wider data buses and multiplexed chip select lines. I'm using it to connect the CPU to the I/O controllers on the auxiliary FPGA.

The epRISC assembler, spasm, is now in the GitHub repository. I haven't changed it at all yet, so it still targets the v4 ISA.

Mostly working, at least. Just finished a few hours ago and aside from a few minor bugs, everything seems OK. I still need to implement the basic-interrupt controller and the single step unit, though, and I'm sure I'll find more bugs over the next few days.

Semi-related note: this marks the first commit where there's something to run! There's a Makefile that uses Icarus Verilog to build a little testbench for the CPU. If you feel so inclined, you can pop your machine code in the testbench's ROM and get a nice trace file of the CPU executing it.

Hello all! It's finally 2017, and with my project due in only a few short months, I have plenty of work ahead of me. Between college applications, work, and school, I've been busy, and I've been moving forward pretty slowly with this project since I finished the board last month. I've also been working on another engineering project for school - a graphing calculator - that's been eating up a lot of my free time (all the sources are on my GitHub if you're curious). On top of all of this, I had another minor setback with the computer - I somehow managed to blow out the regulator, and although the rest of the board is fine, I had to solder in another regulator, which put everything out of commission for a week or so.

I'd like to start updating this log at least once weekly. Now that the hardware is working again, I've dived into the CPU, and since it's all code (in various forms) from here on out the pace of development should pick up. As usual, all the changes will be available on the GitHub repository linked here, so make sure to check there for up-to-the minute updates.

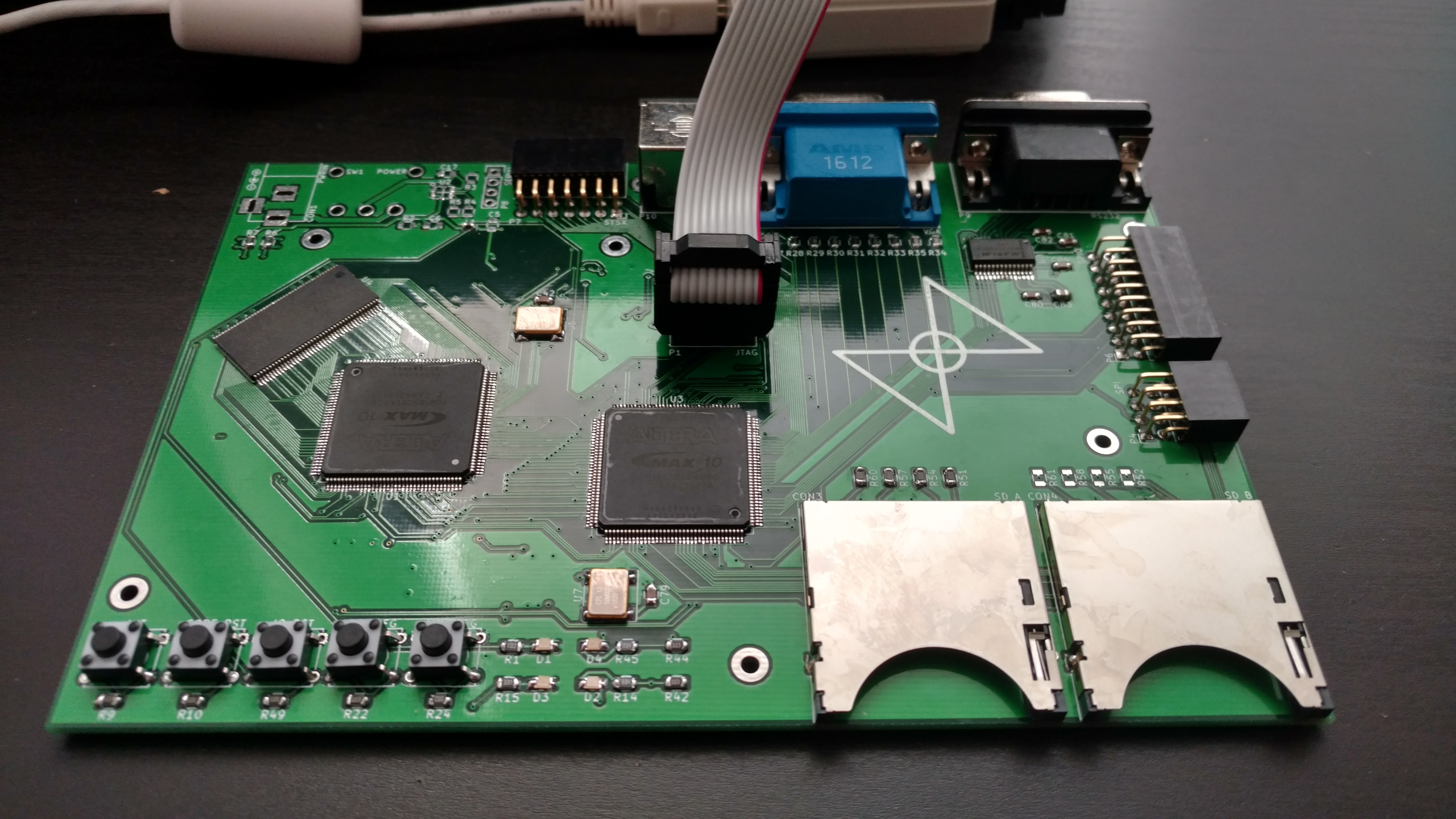

It's been a busy month. Finding time to assemble the prototype has proved difficult, but after a few setbacks and a seven-hour stretch of soldering yesterday, the first board has been completed.

Mostly completed, that is. I forgot to order the voltage regulator, so the top left corner of the board is unpopulated - something I'd like to have fixed by later in the week. I'm testing it with an external power supply right now, and everything looks good; the chips are detected by Quartus and I can program them without issue, although they aren't doing much at the moment.

Otherwise, it's been a slow month progress-wise. I've mostly been working on the ISA and its implementation, both of which should be done by the end of the month.

The PCBs have arrived, and they look great. I normally use DirtyPCB for my boards, but I tried EasyEDA for this run and I'm quite pleased - $90 for six 100x150mm four-layer boards, plus four-day shipping.

I'm planning on assembling them over the next few weeks. I have very limited experience working with SMD components, and even then only with fairly large components, so I'm going through a few practice kits before I try my hand at the real thing. In the meantime, I'm still working on v5 of the ISA, which hopefully will be more-or-less locked in by the time this board is up and running.

The computer being designed here is centered around the epRISC ISA, a custom 32-bit RISC instruction set architecture that's been in constant development for a little over a year. Version one of the computer implemented v4 of this ISA - the first to be functional enough for its intended use. Version two of the computer was also slated to use the v4 ISA, with a few minor tweaks to boost performance and fix outstanding bugs. With the boards still on their way from the manufacturer, I've been spending my time editing the ISA.

At first, it was fine. A few more arithmetic instructions here, a clarification to interrupt behavior there, and so on. But I soon realized that there were a few things that couldn't really be fixed without ripping up something bigger above it, and when I went to rework those objects they revealed even bigger architectural problems. Slowly, the changes added up, until I realized that I was essentially starting over. So I did.

The current version of the ISA is now v5. It's primary goal is to correct the problems that made v4 hard to implement or use, such as:

The changes aren't final yet, but if you'd like to see where things are headed, everything's available in the GitHub repository.

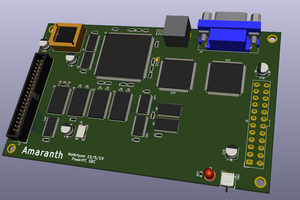

Title says it all - just placed the order for version two's PCBs and feeling cautiously hopeful. The hardware on this board is a major step up from the last:

Everything will be here in a week and a half - plenty of time to start refreshing the CPU implementation - and then it's on to assembly and the inevitable cycle of debugging.

The version documented here right now is the first version, developed from February to July 2016. It includes:

Excluding the SDRAM controller, everything above has been designed, implemented, and/or written by me.

The files currently hosted here are from this version of the project. Be warned: they weren't written for public release and thus probably leave some vital bits of information out. The CPU core is especially buggy, and while it works, it'll probably need to be rewritten for version two.

Create an account to leave a comment. Already have an account? Log In.

Become a member to follow this project and never miss any updates

Ross Bamford

Ross Bamford

Vladislav Mlejnecký

Vladislav Mlejnecký

Tobias Rathje

Tobias Rathje

Carson Herrington

Carson Herrington