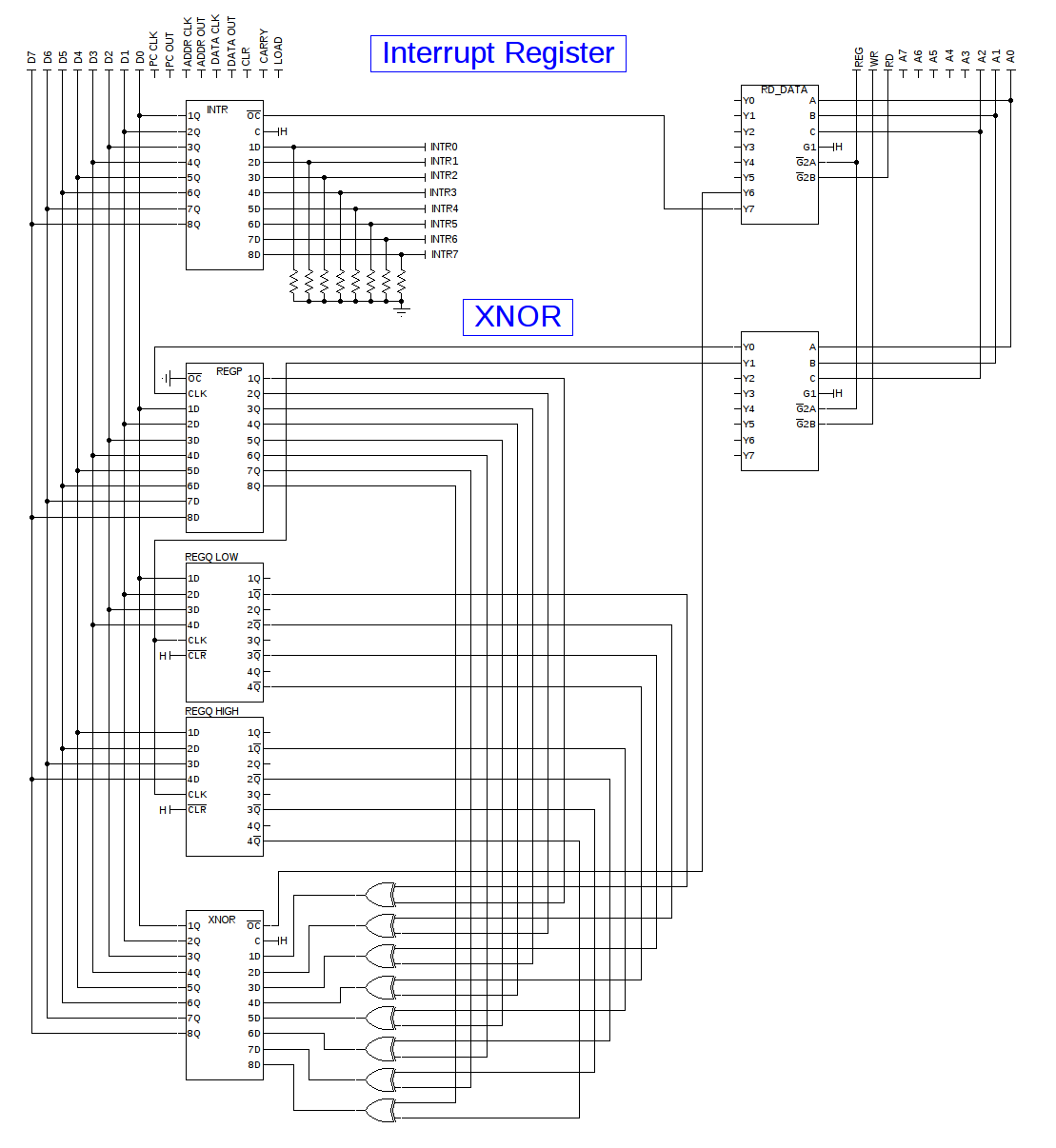

XNOR

One way to squeeze an interpreter and monitor into 128 bytes is to add a helper code. The one to add is XNOR, it will free up 28 bytes (currently 40 bytes).

This could be added to the existing Weird CPU board stack. Should be able to fit the interrupt hardware as well:

Ignoring the design time, making these stripboards takes about six to eight hours of cutting tracks and soldering. And there are always mistakes. So I am not that keen unless it actually "opens up new doors" for the TTA8 concept.

So I guess I should have a go at coding a new monitor.

Well yes the Interpreter and the Inline code fits but not enough room for Call and/or return. I could have worked this out before I started but sometimes you need to do it by hand to kill (or work out what you really want) the option properly.

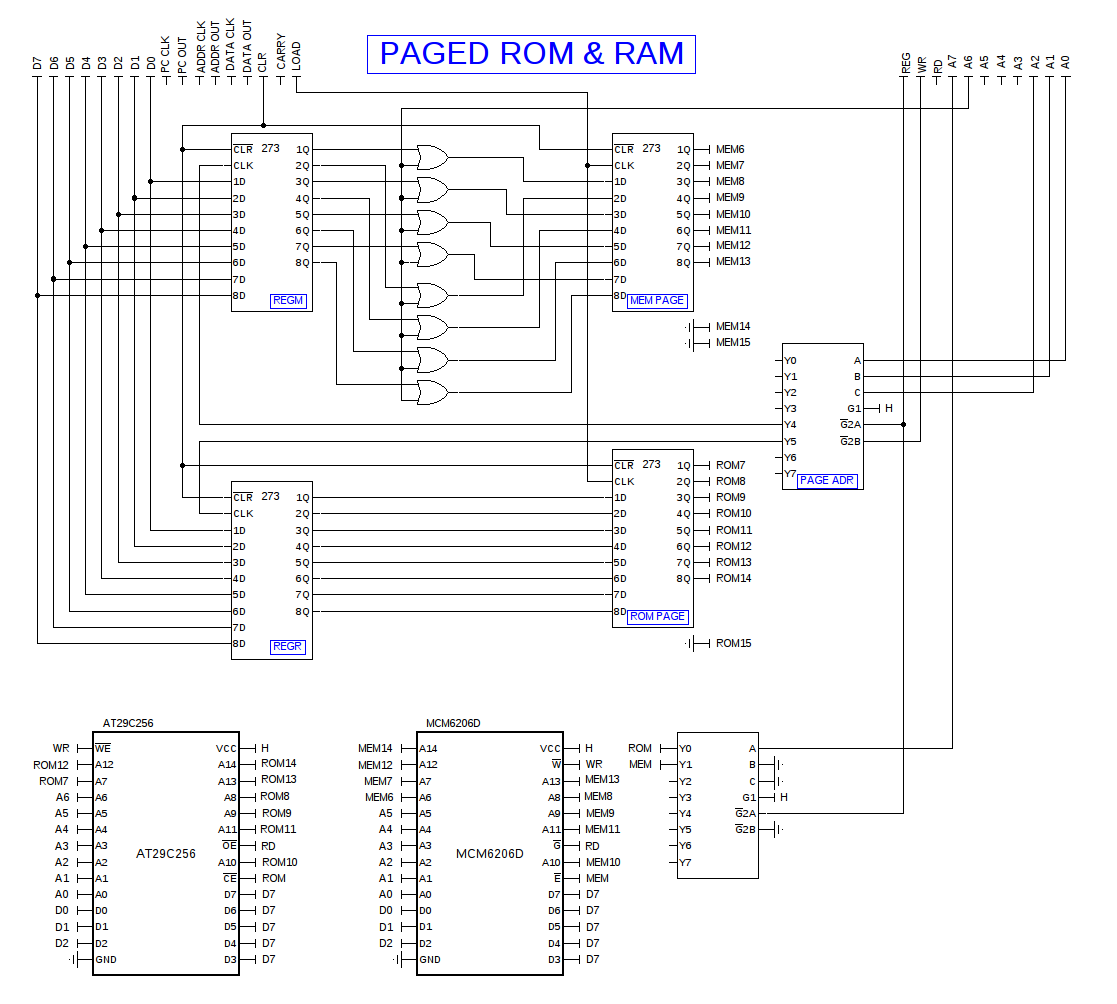

Memory Paging

If stay with 8 bits then memory paging is now the only option. For memory paging the ROM (0x00 to 0x7F) can be completely swapped out. For RAM only 0x80 to 0xBF (64 bytes) can be swaped out as the top half of the RAM (0xC0 to 0xF7) needss to remain visable at all times as it is the CPU model and stack. The same with the hardware registers (0xF8 to 0xFF).

The other "trick" is that the page change should occur on a jump, not when the page register is set.

Here is my design:

The design can access 32kb of ROM and 16kb of RAM.

The main downside is that all memory addresses are two bytes instead of one byte.

If I go down the TTA8 with memory paging I would be looking at a PCB design.

I posted the full TTA8 schematic (image) to my files area (but I will kill the XNOR circuity shortly).

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.