The original EDSAC had two conditional jump instructions (and no unconditional one!), namely Jump if Accumulator >= 0 and Jump if Accumulator < 0. For implementing these, I added a new MISC value called JUMP and two new UBCOND values for testing the SIGN output of the ALU, called BSGN0 and BSGN1.

However, I didn't want to actually use these to perform microcode branching, because then a jump instruction would require up to two cycles, one to test the sign bit and one to load the PC if the test is true. To save a cycle, I arranged things so that JUMP suppresses microcode branching and instead activates a new signal LDPC during T17 if the microcode branch condition is true. This allows the jump to occur at the end of the same cycle that tests the sign.

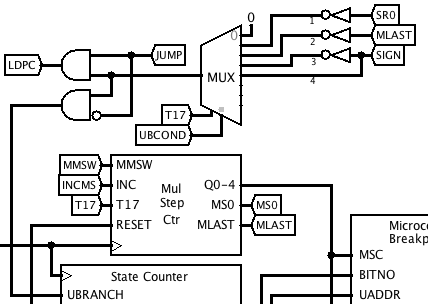

The microcode branch condition circuitry now looks like this:

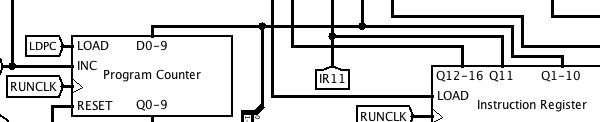

LDPC causes the program counter to be loaded from the address field of the instruction register:

LDPC causes the program counter to be loaded from the address field of the instruction register:

Here is the microcode for the jump instructions. Each one consists of just a single microinstruction that passes the accumulator through the ALU and activates JUMP together with the appropriate condition.

Here is the microcode for the jump instructions. Each one consists of just a single microinstruction that passes the accumulator through the ALU and activates JUMP together with the appropriate condition.

JUMP = 010 # Conditionally load PC from address field of instruction BSGN0 = 110 # Sign FF = 0 BSGN1 = 001 # Sign FF = 1 # E - Jump if accumulator >= 0 00011 0 0001 : - EOI 11 XAC - Y0 CY0 -- - - MSW LSW - - - JUMP - BSGN0 ---- # G - Jump if accumulator < 0 11011 0 0001 : - EOI 11 XAC - Y0 CY0 -- - - MSW LSW - - - JUMP - BSGN1 ----

Update to Transfer and Clear instructions

While doing some more research into the EDSAC, I realised that my implementations of the Transfer and Clear instructions weren't quite right -- they were only clearing the parts of the accumulator that were being written to memory, whereas they are supposed to clear the whole accumulator. I've fixed them, but it means they now take 4 cycles to execute. This is annoying, but there doesn't seem to be anything I can easily do about it.

# T - Transfer and clear 00101 0 0001 : - - 00 XAC CMX YAC CY1 WAC - - - LSW - - - --- - --- ---- 00101 0 0010 : - - 10 XAC CMX YAC -- WAC - - - - - - - --- - --- ---- 00101 0 0011 : - - 01 XAC CMX YAC -- WAC - - - - - - - --- - --- ---- 00101 0 0100 : - EOI 11 XAC CMX YAC -- WAC - - MSW - - - WMEM --- - --- ---- 00101 1 0001 : - - 00 XAC CMX YAC CY1 WAC - - - LSW - - - --- - --- ---- 00101 1 0010 : - - 10 XAC CMX YAC -- WAC - - - - - - - --- - --- ---- 00101 1 0011 : - - 01 XAC CMX YAC -- WAC EVN - - - - - WMEM --- - --- ---- 00101 1 0100 : - EOI 11 XAC CMX YAC -- WAC ODD - MSW - - - WMEM --- - --- ----

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.