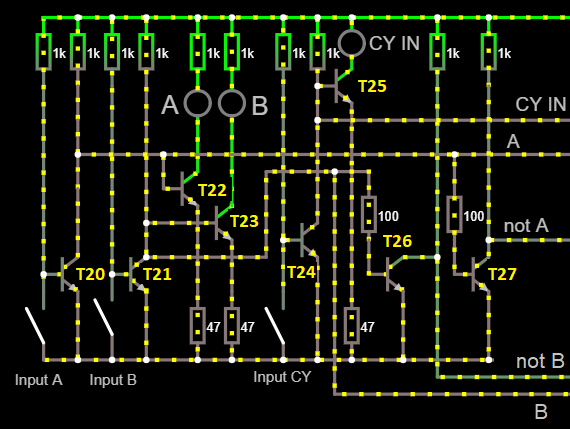

The full ALU design also has two parts in the schematic, the first part creates the input signals again, main difference is that now also the A signal is available in complement form:

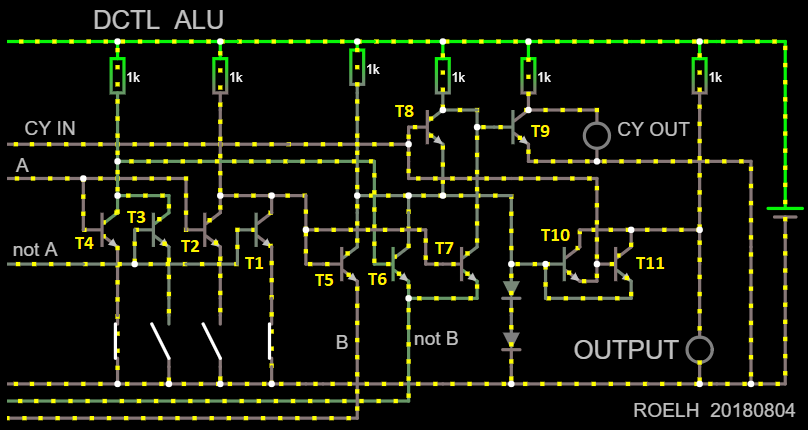

And the following part is the actual ALU. The ALU needs both straight and inverted inputs for A and B. Since these are probably already available (because the flipflops in the CPU will have both outputs), the inverters of these signals are not included in the transistor count of the ALU.

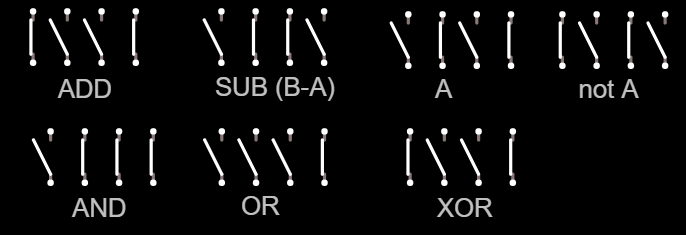

At the lower left side, you see four switches that control the function of the ALU. The switch positions for the main functions are:

In reality, the switches should be replaced by transistors. These transistors can be in common for several bits (4 bits or perhaps even 8).

One thing must still be added to the ALU, that is a transistor that forces the input carry to zero for the logical functions. That makes it a 12-transistor design. So in this simulation, the CY-IN must be set to zero for the logic functions.

Although only seven functions are shown for the switches, the four signals can select every theoretical possible function of two binary inputs. This includes inverted versions of AND, OR and XOR, and the input B and inverted B.

The simulation can be quite surprising. Did you know that a bipolar transistor can also work backwards (current flowing between emitter and collector in opposite direction) ? This actually occurs in a certain input arrangement, but it did not have an effect on the logic output.

Not mentioned yet.... supply is 5 volts. The transistors are general NPN transistors that are available in the simulator.

This is a ripple carry adder. The carry signal has to pass T8 and T9. If this is not fast enough, I would at first check the influence of the circuit that is connected to the emitter of T8. The carry could also be made two times faster by calculating it for two bits at a time.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Hi, nice experiment, fascinating logic. Is SUB(B-A) the same as XNOR? Because that's what the truth table looks like to me. The truth table I get is:

A B O

0 0 1

0 1 0

1 0 0

1 1 1

Are you sure? yes | no

Yes, it is the same as long as the input carry is zero. You might find this link:

https://hackaday.io/project/160506-4-bit-ttl-alu/log/157734-more-about-subtraction

helpful, that tells how subtraction is derived from addition.

Are you sure? yes | no