I’m now 4 weeks in to the project and still don’t have a finished design. I’m getting close though and have finalized the design for the GPU. I’ve added the chips to the components list to give an idea of the size and complexity of this section. The components list will be expanded in the future, so for now it just details the 20 chips used exclusively by the GPU (not shown are the RAM and ROM chips since these are equally shared by the CPU).

The CPU design is tracking towards 25-30 TTL chips. I’m hoping to have this part of the design finished within the next two weeks. This means the final design will have somewhere between 45-50 TTL chips. Along with these are the RAM, ROM, RS232 line driver, analog switch (already listed and used to switch between video DACs), and an op-amp for a proper Sallen-Key filter used by the audio DAC. Including these brings the YATAC in line with a typical IBM PC video card of the early 80’s with over 50 chips.

One of the biggest challenges with the design is the speed at which things need to operate. The last stage of the GPU uses the VGA dot clock of 25.175 MHz. This doesn’t pose too many issues since the control logic is fairly simple in this area. This clock is divided down to 12.5875 MHz and is used to switch the context of the address busses between the GPU to CPU. Each cycle lasts a little over 79 nS and only provides 12 nS each side of the 55 nS memory access to tri-state each address bus, set up a data latch, clock, then hold the data. This can be done, but requires a fully synchronous design and the fastest TTL chips available.

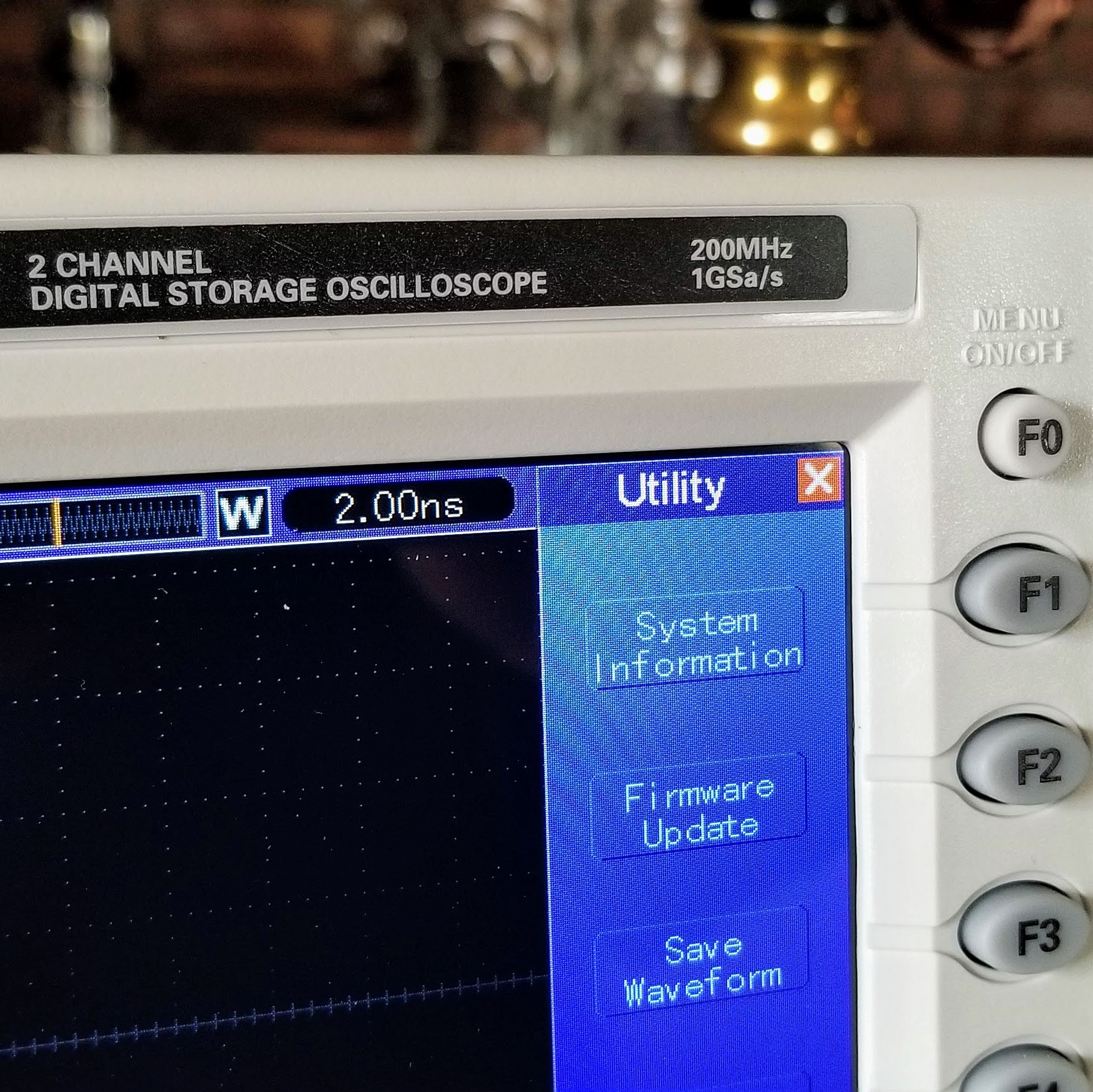

Needless to say, I’ve made some upgrades to my test equipment before I attempt the prototype!

Alastair Hewitt

Alastair Hewitt

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.