Over the past weeks/months/too much time, I have been primarily occupying myself with the details of the "Alice" chipset, as this is the magic sauce that will make Tomodachi X2 either awesome or not so cool. Details such as how to switch between system modes, how to make everything flexible enough that one isn't limited to just a handful of options, and maybe most importantly of all, what 'native Tomodachi mode' is all about.

While brainstorming about this both by myself and with some friends, it quickly became obvious that while one could totally use one or more of the hardware CPUs on the board for native mode, it would be easier and much more powerful to use a more modern architecture. That's when picking a RISC-V core came into the picture.

These cores are nice and small, with some taking up only a few thousand LEs on an FPGA like the ECP5. Meanwhile they are efficient (depending on the core in question, of course) and very flexible due to the RISC-V architecture. This led to us poking at a number of cores, including f32c, Rocket and a funky one called Potato. Depending on which of these are the least painful to use, and with a strong preference for VHDL will ultimately decide which one will be featured on the first functional TX2 prototype.

Best thing of course is that since they all use the RISC-V ISA, switching cores later on is totally cool, as the software will still run.

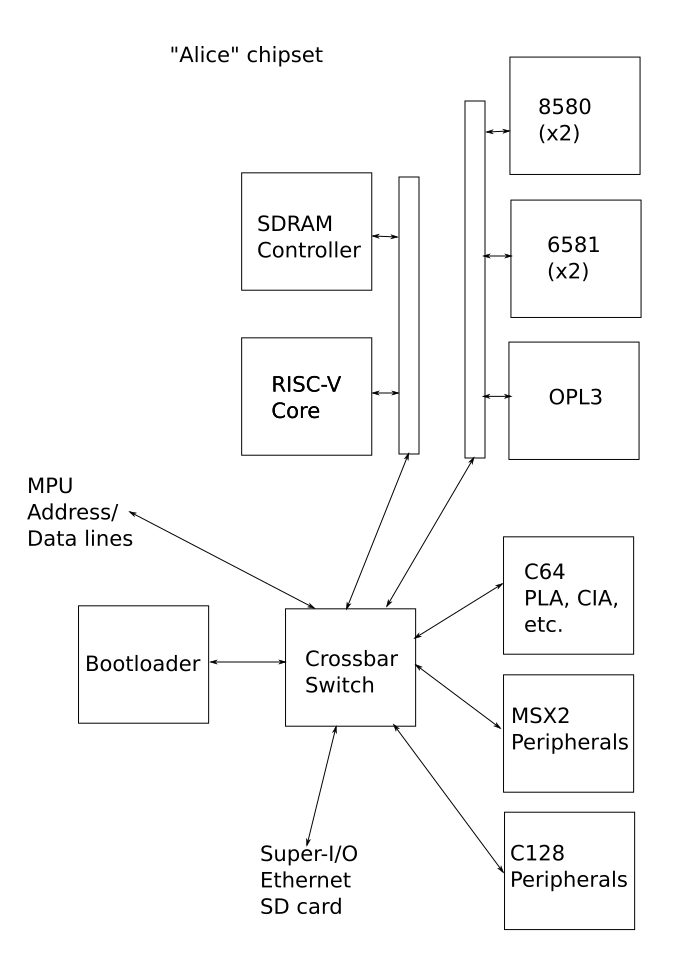

As for the architecture of the chipset itself, it'll likely end up looking somewhat like this:

Using a crossbar switch fabric to tie relevant elements together, and likely splitting mode-specific peripherals (such as the C64 PLA, ROMs and CIA chips) into their own modules should provide maximum flexibility. Meanwhile the SDRAM controller (DDR3 or otherwise) would be designed to accommodate different modes, such as 16- or 24-bit addressing, even allowing each MPU to have its own dedicated block of RAM, up to 64 kB or 16 MB.

As far as mode selection goes, one might be reminded of the C128, where one had to remember in which mode one was, followed by performing the required ritual steps to boot into the other mode: C128 manual.

Here a thought is to either boot into native mode, and execute a command there that will perform the switch, or have physical switches (hooked up to the bootloader in the FPGA) that can set the desired mode before one powers up the system. Perhaps a tad Altair 8800-ish, but could be useful if one intends to use the system in a specific mode for an extended period of time.

Maya Posch

Maya Posch

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.