Whew! Apologies for the long delay - I was working on this on-and-off, and struggled on the new Digilent Cmod-A7 I got in a cheap price from a local store (they are doing stock clearence).

Unfortunately, I had been also wrestling on the Xilinx Vivado toolchain, and it looks like it hasn't been quite nice to me. I've asked around in Digilent, and lucky me they are helpful enough to get a simple project to be compiled: https://forum.digilentinc.com/topic/18479-cmod-a7-vivado-2019-cannot-get-past-implementation/

Also, unlike the Intel Quartus ones, I couldn't add 74 logic blocks inside their system board, and had to fabricate my own 74245 + 74373 glue logic in Verilog instead.

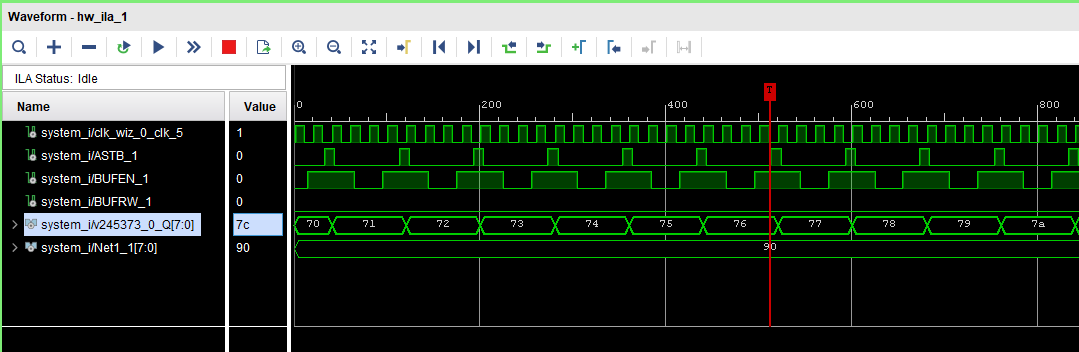

Even compiling it could be painful - 5 minutes and I ended up simulating on the most part of the design. Finally, I got this to catch the lower address without using 74373 and 74245! (all inside the FPGA)

All is not done yet, and I'm doing my best to make it run a simple program. As usual, the logic analyzer output shows the 8088 reading 0x90 (NOP) from FPGA and the FPGA latches the bottom half of the address each strobe.

Note: For the previous log, I had found out that Cyclone 2 doesn't have libraries or Nios part to directly connect the SDRAM to some other peripherals. This only exists in newer Cyclone models, so I had to use the Digilent Cmod-A7 I got from a stock clearance sale instead.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.