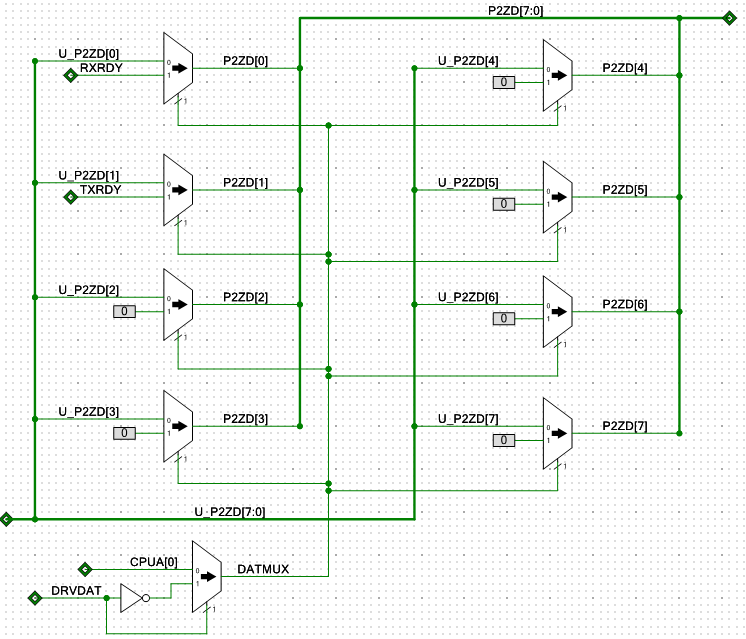

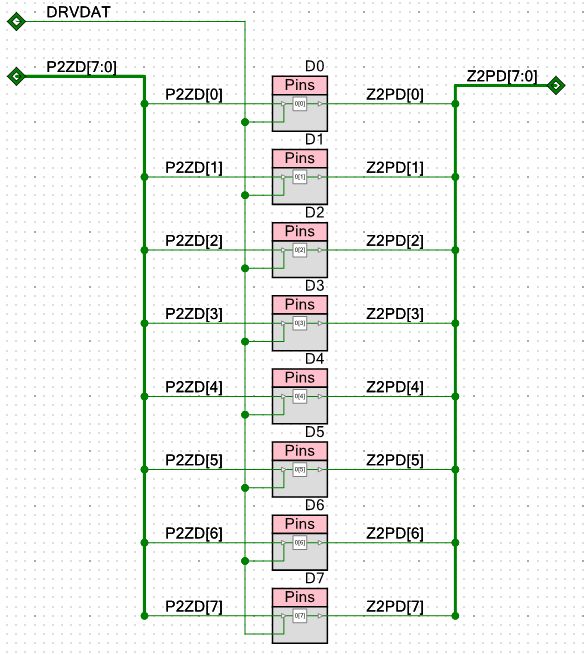

The Z80 needs to be able to read the (PSOC to Z80) data register and status register. This requires a read multiplexer. Here's the path for the Z80 Read Data lines:

The bits of the status register are:

D0 = Receive Data Ready

D1 = Transmit Data Ready

D2-D7 = 0

The data bus pins to/from the Z80 are bidirectional. I've chosen to name the pins similar to SPI bus notation. P2Z is PSoC to Z80 and Z2P is Z80 to PSoC. Hopefully this will minimize confusion.

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.