I had a bug on SRAMA11. It manifested as an inability to set the line high. Actually, it was connected to SRAMA12 and when SRAM12 went high SRAMA11 also went high. Was incredibly easy to fix.

Problem manifested as a bad dump of the ROM file. I am using Grant's ROM.HEX file converted to a C array. Dumping at 0x0000 showed data from somewhere else. Board was passing SRAM test but the test looped data every 256 bytes. For some reason the address line shift test was passing (need to figure that out still).

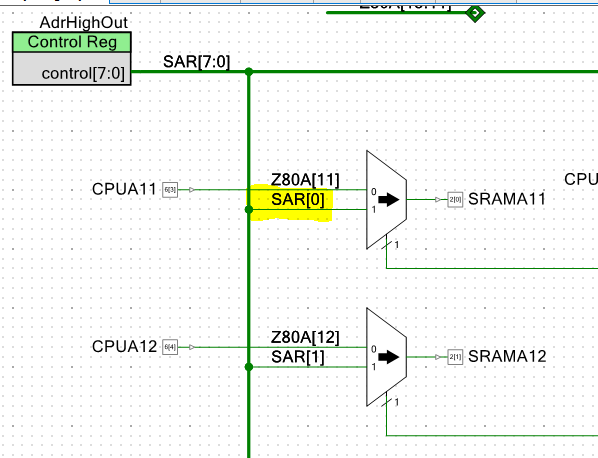

Used Front Panel to set one address line at a time. Set the address I wanted with the LDADR button on the front panel. Looked with the scope at the affected address line. Found that SRAMA11 was tied to SRAMA12. It wasn't a short on the board, it was an error on the banking page of the schematic. This is the bit fixed but it was set to SAR[1] so it was replicating SRAMA12.

Now the dump of the ROM works. At least the first few locations look right. Need to check some additional locations to verify they work.

Using Grant's 9-chip ROM.HEX file. The file has both the basic and monitor in one 8KB ROM. From Grant's page:

ROM contents ROM.HEX (all that is needed to program the ROM. Contains the BASIC.HEX and MONITOR.HEX)

Next step is to design the SIO emulator.

Running Grant's code I am not seeing any IORQ* strobes. I think I should be seeing IORQ* strobes.

I need simpler IO code.

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.