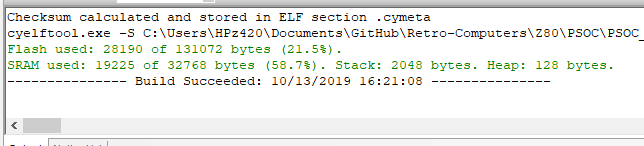

The PSoC compile shows:

The SRAM is more than half used. This is because the C compiler thinks that the ROM monitor that is downloaded to the Z80 is an array that can be changed. To keep the ROM monitor in EPROM and not copy it to RAM, use the keyword const:

const unsigned char monitor_eprom[] =

{

0xF3, 0xC3, 0x8A, 0x01, 0x00, 0x00, 0x00, 0x00, 0xC3, 0x24, 0x01, 0x00,

0x00, 0x00, 0x00, 0x00, 0xC3, 0xC0, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00,

...

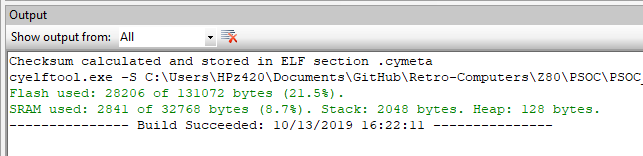

After that change, the resources are:

That frees up 16K of SRAM (half the internal SRAM of the PSoC) and only cost 16 more bytes of ROM.

There is still a lot of free space in the PSoC for additional logic.

------------------------------------------------------------

Technology mapping summary

------------------------------------------------------------

Resource Type : Used : Free : Max : % Used

============================================================

Digital Clocks : 3 : 5 : 8 : 37.50 %

Analog Clocks : 0 : 4 : 4 : 0.00 %

CapSense Buffers : 0 : 2 : 2 : 0.00 %

Interrupts : 9 : 23 : 32 : 28.13 %

IO : 65 : 7 : 72 : 90.28 %

Segment LCD : 0 : 1 : 1 : 0.00 %

I2C : 1 : 0 : 1 : 100.00 %

USB : 1 : 0 : 1 : 100.00 %

DMA Channels : 0 : 24 : 24 : 0.00 %

Timer : 0 : 4 : 4 : 0.00 %

UDB : : : :

Macrocells : 32 : 160 : 192 : 16.67 %

Unique P-terms : 52 : 332 : 384 : 13.54 %

Total P-terms : 53 : : :

Datapath Cells : 0 : 24 : 24 : 0.00 %

Status Cells : 4 : 20 : 24 : 16.67 %

Status Registers : 3 : : :

Sync Cells (x2) : 1 : : :

Control Cells : 9 : 15 : 24 : 37.50 %

Control Registers : 9 : : :

Comparator : 0 : 2 : 2 : 0.00 %

Delta-Sigma ADC : 0 : 1 : 1 : 0.00 %

LPF : 0 : 2 : 2 : 0.00 %

SAR ADC : 0 : 1 : 1 : 0.00 %

DAC : : : :

VIDAC : 1 : 0 : 1 : 100.00 %

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.