This design is still very early, but I'm planning to draw design elements from my previous (unfinished) 68000 homebrew computer project, so for the moment I'm assuming a similar design aside from the CPU choice and will adjust as needed as I dig into the details.

The high-level design includes:

- A RV32I CPU core in an ICE40 FPGA, wrapped in an external memory bus similar to the 68SEC000 MPU and a very simple MMU of my own design. Might implement the RISC-V privileged ISA itself or a simplified model; not sure yet.

- A generous but not excessive amount of SDRAM as working memory.

- A simple operating system in ROM.

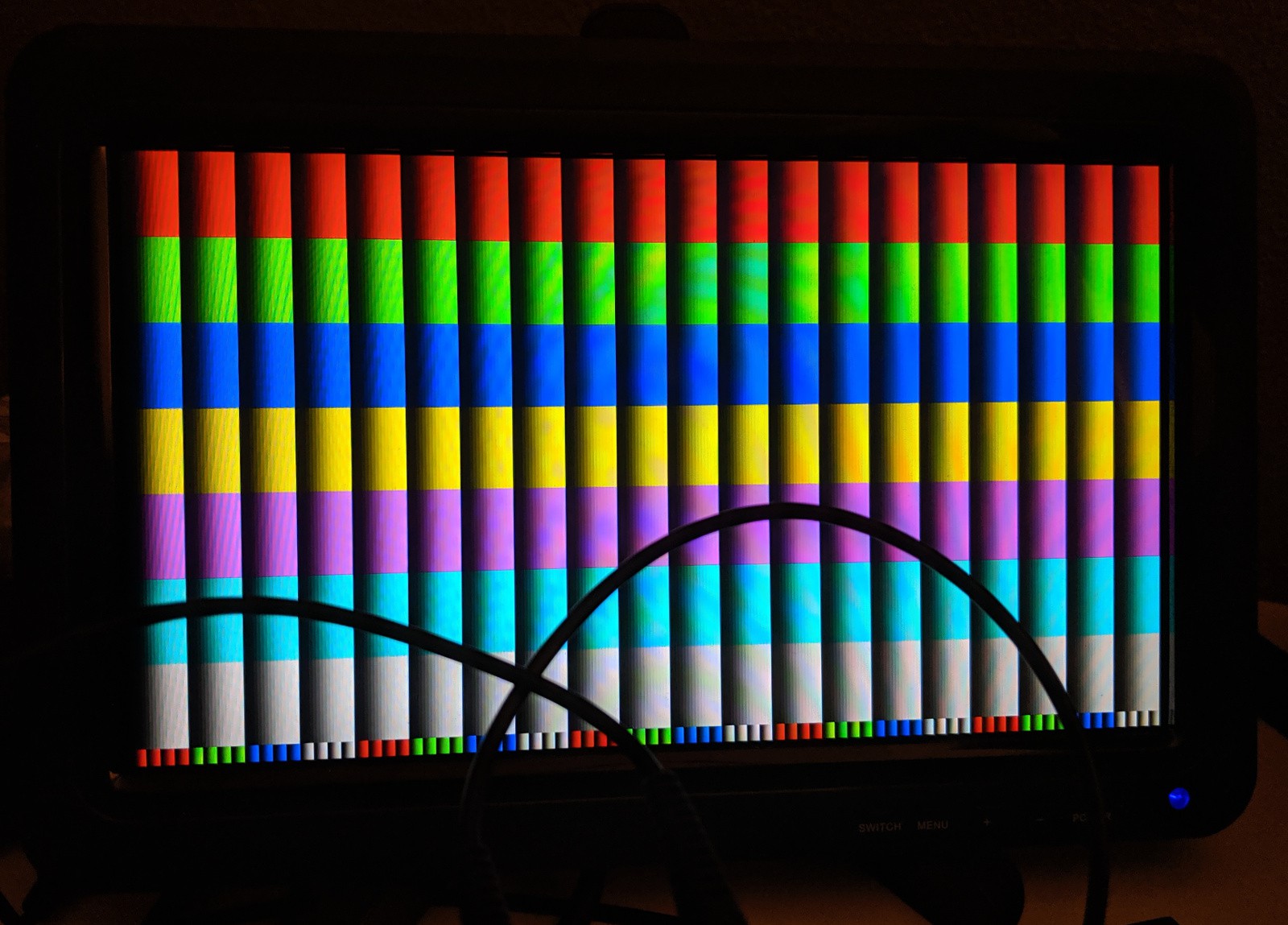

- 12-bit-per-channel 720p DVI video output via another ICE40 FPGA and some dedicated video RAM.

- A rather incongruous small ARM microcontroller both as a bootup controller (to load the FPGAs) and as a straightforward interface to external buses, hopefully including USB but might end up using simpler buses like PS/2 in the end.

So far I have only very early prototypes of all of the above, some of which are still embedded in the former 68000 computer project and awaiting adaptation. This project is definitely a labor of love and I'll be surprised if it ever reaches a point I could call "finished".

Martin Atkins

Martin Atkins

Blair Vidakovich

Blair Vidakovich

Dylan Brophy

Dylan Brophy

Jon Thomasson

Jon Thomasson