The #YASEP Yet Another Small Embedded Processor is currently in "shelved" state while I develop the low-level aspects of #YGREC8. But the YASEP has taught me a lot of important lessons that I want to preserve and annotate, some of them 12 years later, before the original server is taken down... The project #PDP - Processor Design Principles owes a lot to the YASEP as well.

It's also an opportunity to back it up as well as correct broken links for example. If I can save 10 logs per day, it would take a week for a complete move to HaD, of a fraction of the confinement period...

Logs:

01. Log#01 : First post \o/

02. Log#02: More flexibility and options for YASEP

03. Log#03: 106MHz !

04. Log#04: New register organisation

05. Log#05: A suitable HW platform for CPU design ?

06. Log#06: No news, good news ?

07. Log#07: Building momentum

08. Log#08 : Open Graphics board needs more preorders !

09. Log#09 : YASEP2009 in preparation

10. Log#10 : YASEP is published under the AGPL

11. Log#11 : The new Colibri board is almost here !

12. Log#12: Site update, architecture modifications, and new FPGA boards

13. Log#13 : How to double the SRAM capacity of a FPGA board ?

14. Log#14 : Barrel Shifter : SHL16 ready

15. Log#15 : Evolution of the instruction set

16. Log#16 : Yet another new Actel toy \o/

17. Log#17 : YASEP2009 : "It's gonna be big"... when it comes

18. Log#18 : Listed : the dynamic LISTing EDitor

19. Log#19 : what about YASEP2009 ?

20. Log#20 : Yet another Instruction Set Architecture change

21. Log#21: First details of the new "extended" long instruction

22. Log#22 : First Layout of a custom FPGA+SRAM board

23. Log#23 : YASEP@HSF2009

24. Log#24 : Probable new features

25. Log#25 : YASEP en français

26. Log#26 : Back from vacations...

27. Log#27 : When you connect the power supply, it works...

28. Log#28 : Support of Alphanumeric LCD with YASEP

29. Log#29 : YASEP2010

30. Log#30 : Fast and secure InterProcess Communications

31. Log#31 : ACTUINO day 1

32. Log#32 : This little Least Significant Bit

33. Log#33 : YASEP2011

34. Log#34 : The YASEP and Defora

35. Log#35 : Register Parking

36. Log#36 : A YASEP assembler in C by DeforaOS

37. Log#37 : Interactive Assembler, take 2

38. Log#38 : microYASEP's first boot !

39. Log#39 : at a glance...

40. Log#40 : 24 bits per instruction

41. Log#41 : Licensing freedom

42. Log#42 : More JavaScript gadgets

43. Log#43 : The social YASEP

44. Log#44 : The old new YASEP site

45. Log#45 : Nikolay's questions

46. Log#46 : The Zero status flag

47. Log#47 : el YASEP en español

48. Log#48 : Virtual Load and Store

49. Log#49 : YASEP@JM2L2012

50. Log#50 : The YASEP goes to Berlin

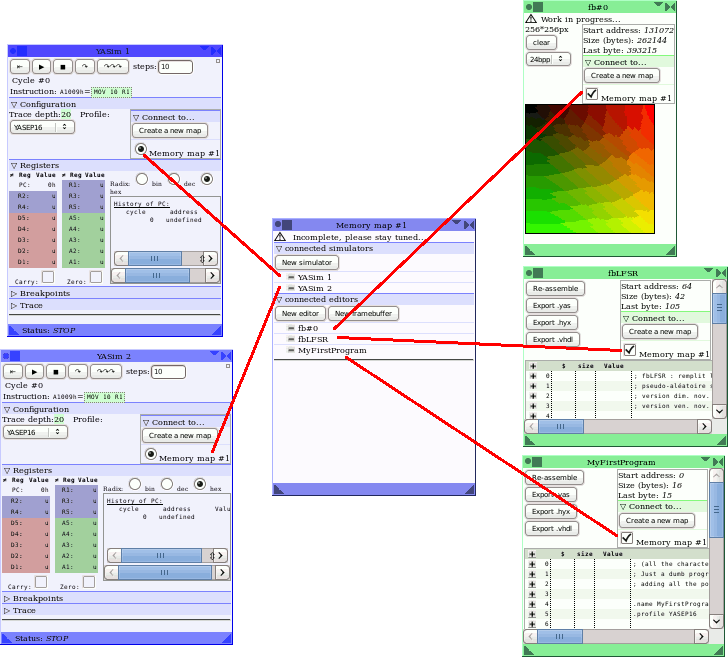

51. Log#51 : YASim is working

52. Log#52 : YASEP2011 is almost finished

53. Log#53 : The YASEP2013 season is open !

54. Log#54 : A crippled YASEP ? It's for your own good...

55. Log#55 : More about the IPC instructions

56. Log#56 : The tracker's backend

57. Log#57 : There is always crazier than you.

58. Log#58 : Project split

59. Log#59 : A new register parking system

60. Log#60 : Definition of the auto-update fields

61. Log#61 : The yasep2014 milestone

62. Log#62 : Zero becomes Equal

63. Log#63 : Flag polarity

64. Log#64 : Why ? Pourquoi ?

65. Log#65 : Baby steps

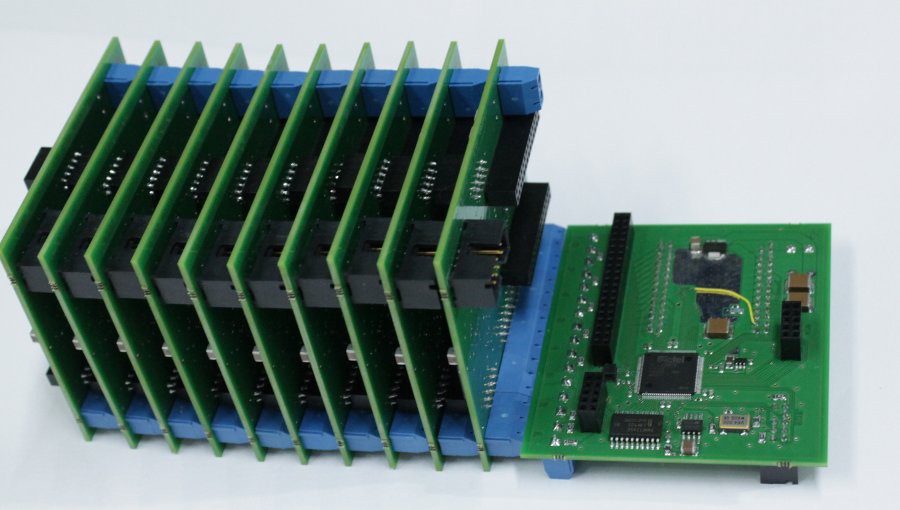

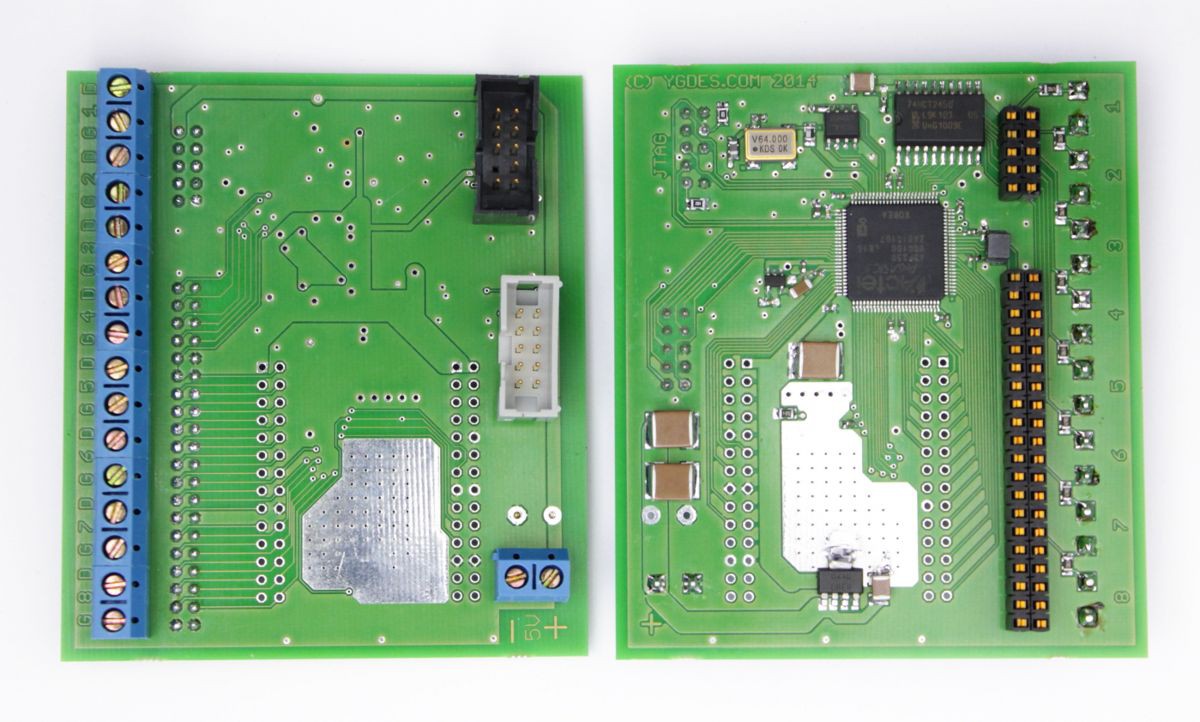

66. Log#66 : The first PCB designed for the YASEP

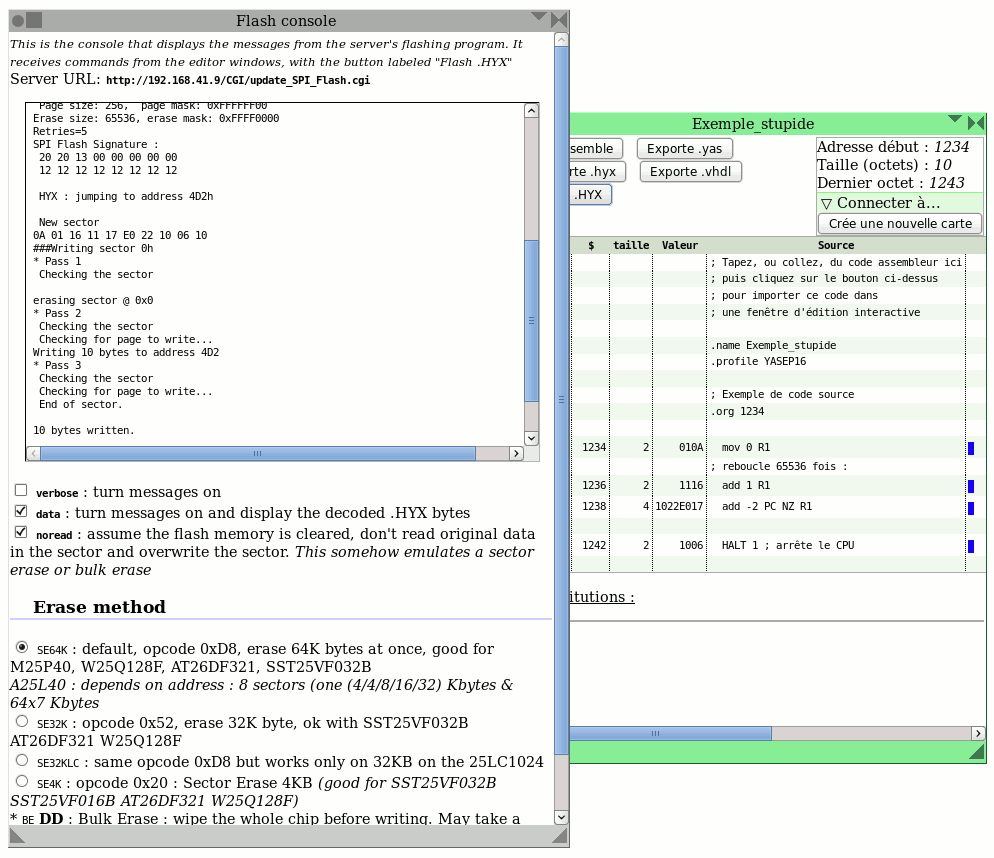

67. Log#67 : The latest tool : direct programming of SPI Flash from the source code editor

68. Log#68 : Latest tutorial

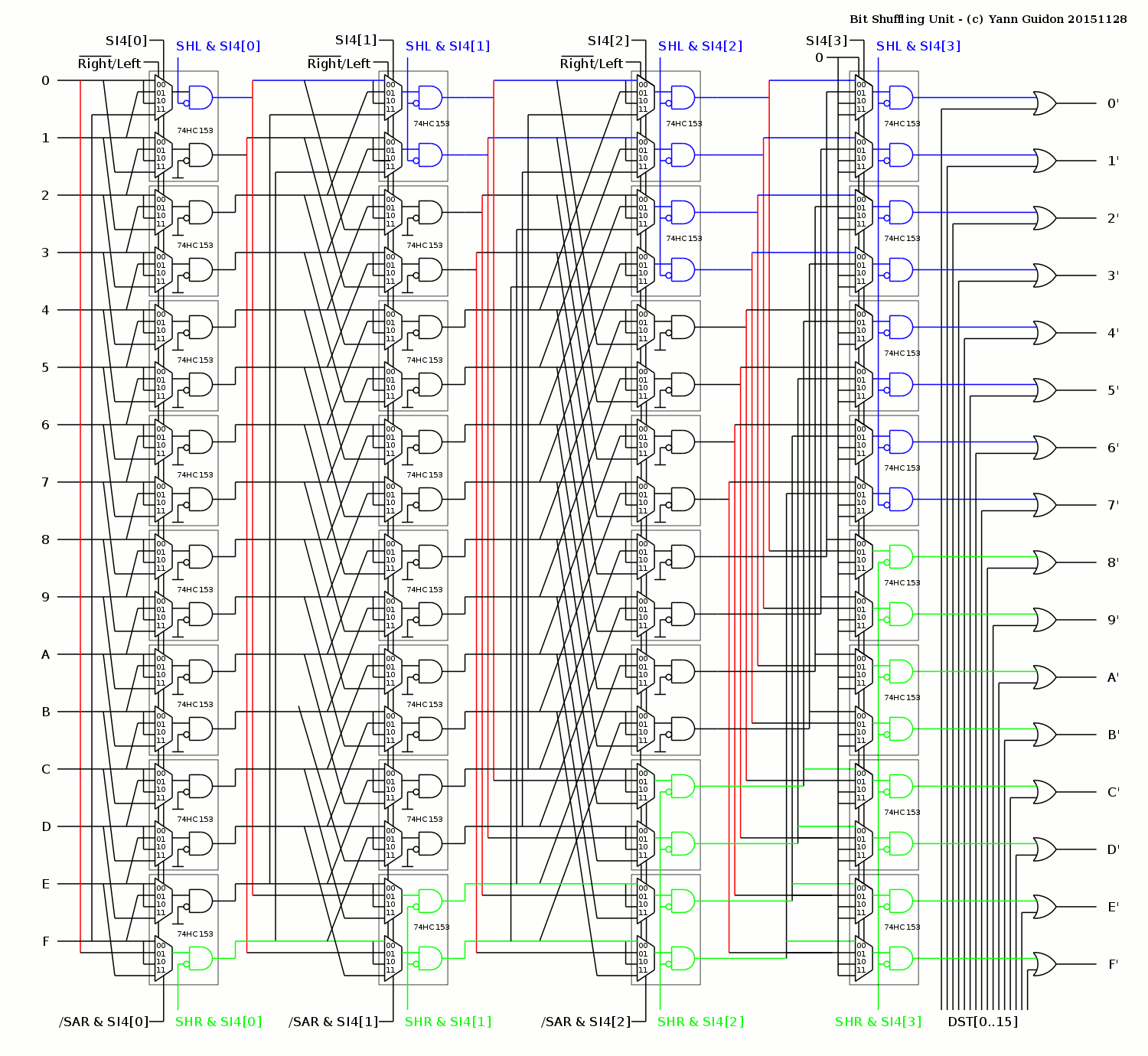

69. Log#69 : yasep2015

70. Log#70 : The Discrete YASEP

71. Log#71 : Progress with the SHL unit

72. Log#72 : The last post

Voilà.

Yann Guidon / YGDES

Yann Guidon / YGDES

Erik Piehl

Erik Piehl