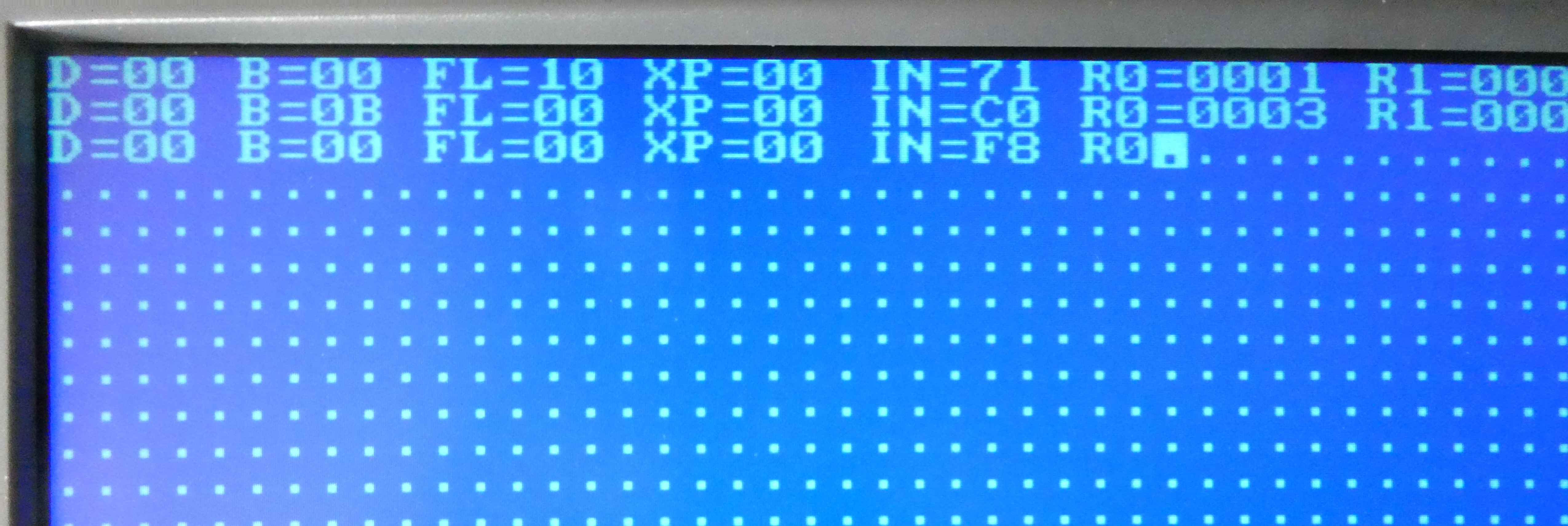

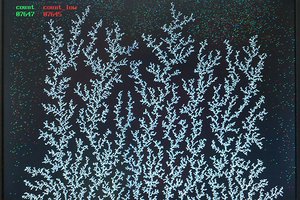

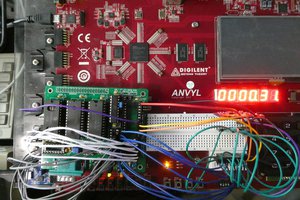

Demo session, uploading the bit file (which is inside the sys_180x*.zip) to Digilent Anvyl board, and running Monitor and Basic. Both the CPU and the TTY to VGA controller have been programmed using the microcode compiler.

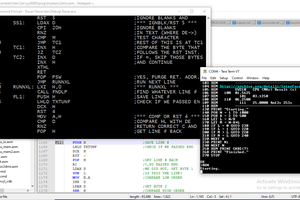

Microcoding for FPGAs

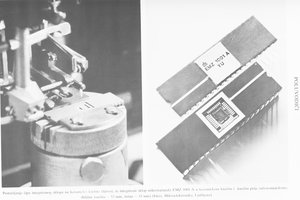

A microcode compiler developed to fit into FPGA toolchain and validated to develop CDP1805-like CPU and text-based video controller

zpekic

zpekic

Bruce Land

Bruce Land

Hi! Yes, Cosmac is really a paragon of simplicity even now, my implementation is totally the opposite but it was done for learning and illustration of reimplementing existing CPUs using my microcode tool chain. In the meantime I improved elements of that and the microcode here could be improved too. If you decide to re-implement, feel free to reach out! Good luck!