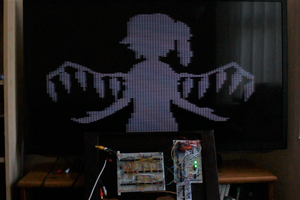

See the YouTube video for more details, where I show the video output and talk through the circuit:

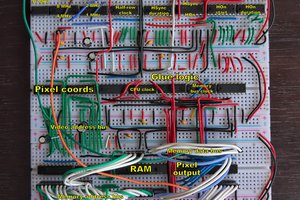

The key simplification from Ben Eater's design is getting rid of all the logic for working out the sync signals and just storing that in the EEPROM instead, along with the image data. It has some effects on the output resolution options, but is very effective at reducing the chip count, making this a very accessible way to experiment and tinker with video output!

Making your own

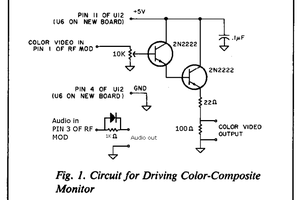

If you want to build this yourself, check out the schematic in the Files section, it's fairly simple. I've also uploaded two Python scripts there - one that converts the source image into stretched, palettized form; and another that generates the EEPROM image, including timing information and the palettized image from the first script.

Refer to the Build Instructions below for more details.

Extending it

There were a lot of compromises to keep the IC count low, which means that if you want to extend the circuit, without worrying so much about IC count, there's a lot of low-hanging fruit.

- Things like increased resolution and better colour depth would be fairly easy to achieve using a second EEPROM and/or different timer logic

- Even higher resolutions could be possible with some shift register magic

- You could also experiment with a palette look-up EEPROM

- It should be possible to replace the EEPROM with SRAM and interface it with a CPU - and if you're willing to cut a lot of corners and put up with some glitches, this should be possible without adding many more ICs

If you do build or extend this circuit, I'd love to hear about it, so please let me know!

Hooking up to a Ben Eater-style 6502 computer

I've added some notes in a Project Log below regarding hooking this up to a BE6502 computer. It's fairly simple and works really well!

Barry Nelson

Barry Nelson

Can you provide the assembler/machinecode for Ben Eaters CPU for running your samples?