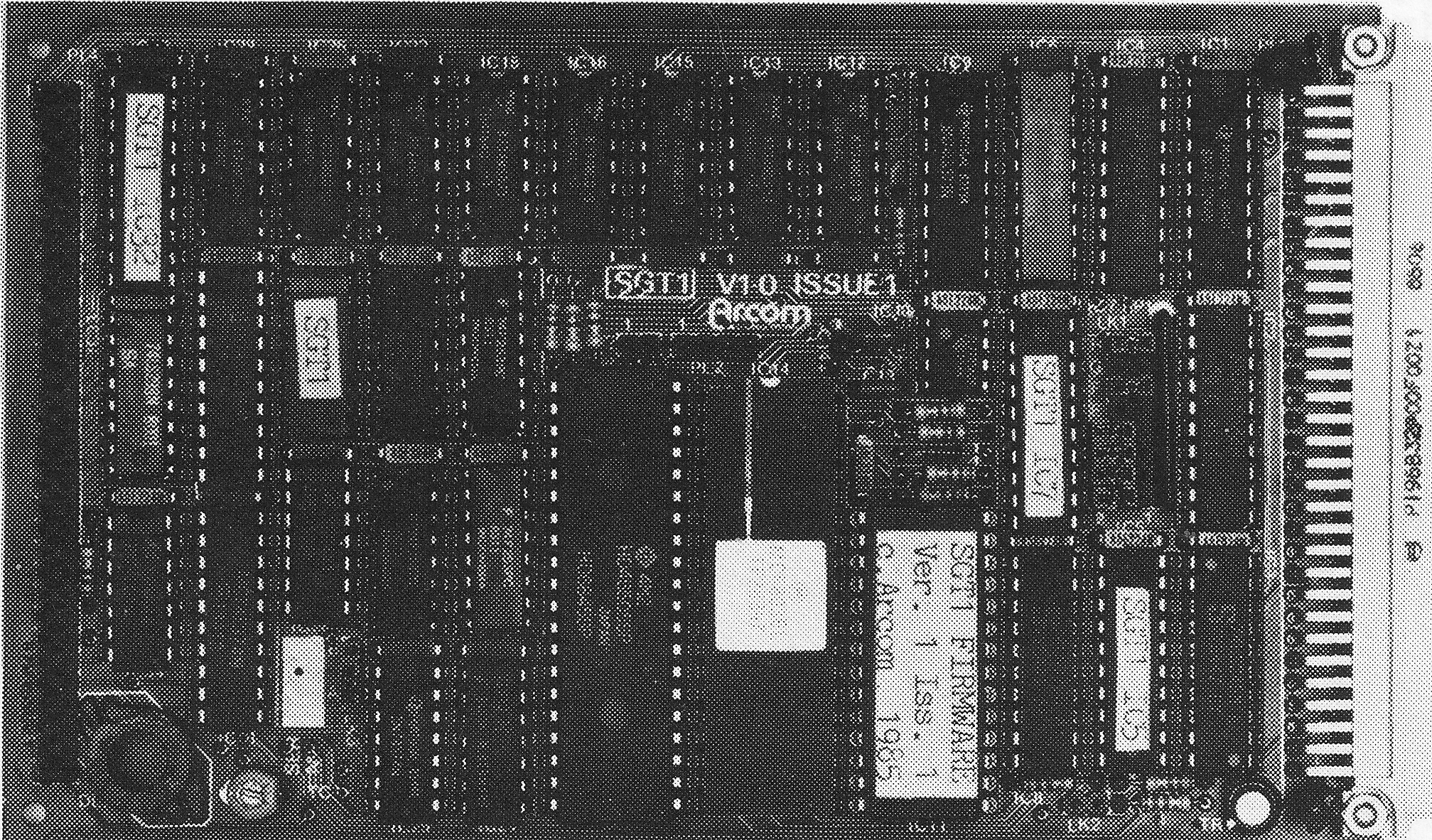

I expected this to be extinct, but Steve told me he had one AND the manuals for the hardware and software! He kindly scanned them for me and very kindly posted the board to me! It is serial number 2 - the second one ever sold!

The software manual includes a listing of the start of the ROM, which shows the names of many variables, jump tables, and the names of functions being jumped to. This is a great help. I have assimilated this into the regenerated source code. The labels have had the '.' character replaced with "_" because my assembler rejected the former.

Keith

Keith

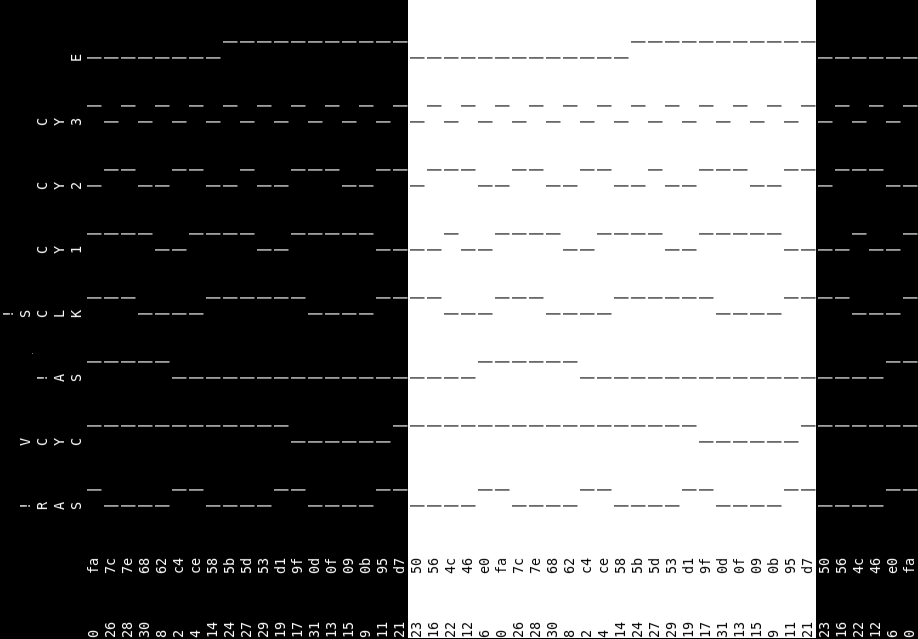

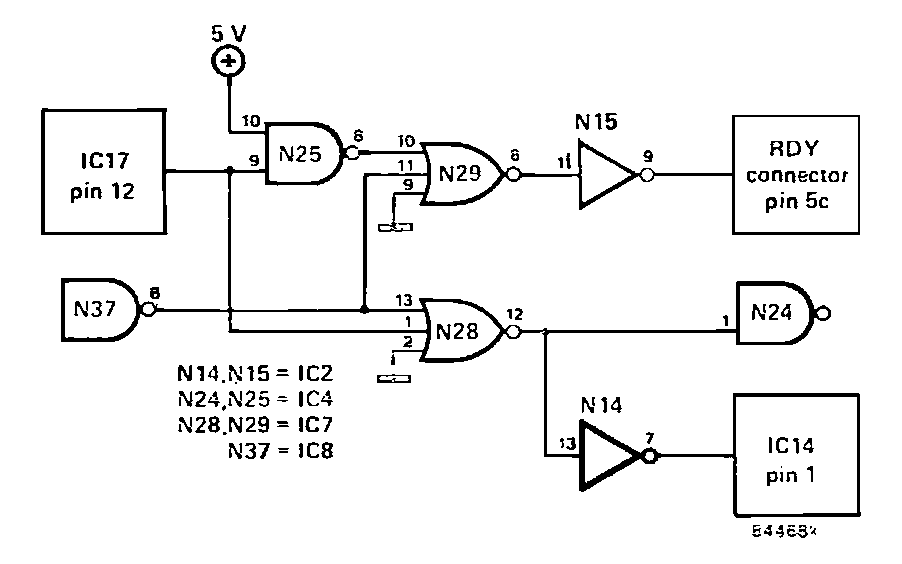

I had a long hard look at the binary sequencing, the see if it could be implemented in a 16V8 GAL.

I had a long hard look at the binary sequencing, the see if it could be implemented in a 16V8 GAL.

Howard Jones

Howard Jones