This project builds upon my previous Intel HEX project which I developed to:

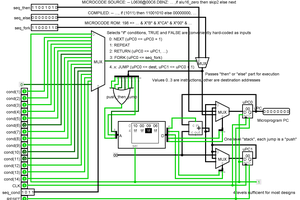

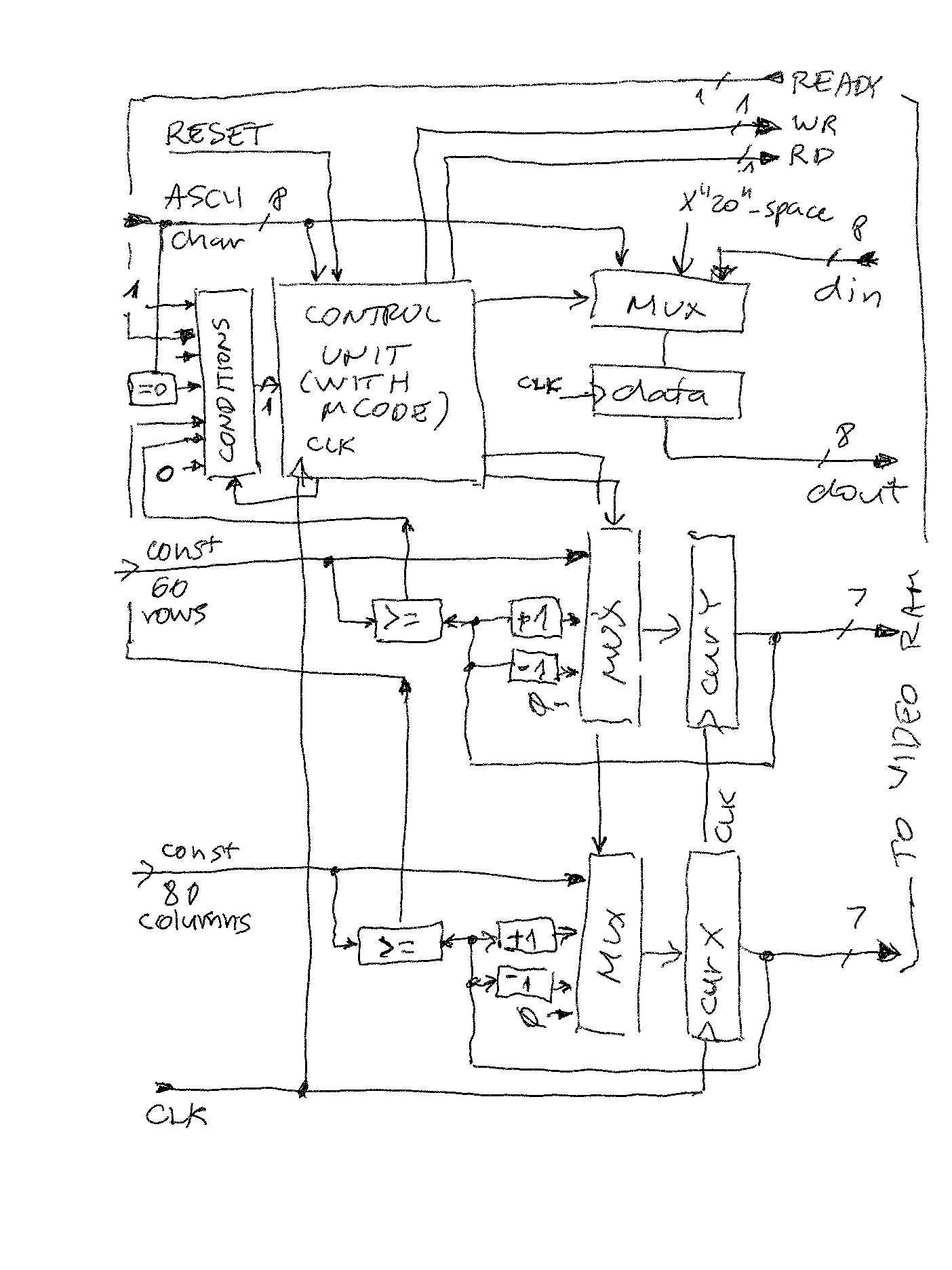

- Check how difficult it is to create non-CPU controllers using microcode

- Improve my microcode compiler based on real project

- Give me a tool for priming memory of FPGA-based computers when CPU is not working / written yet - during runtime, avoiding slow recompiles

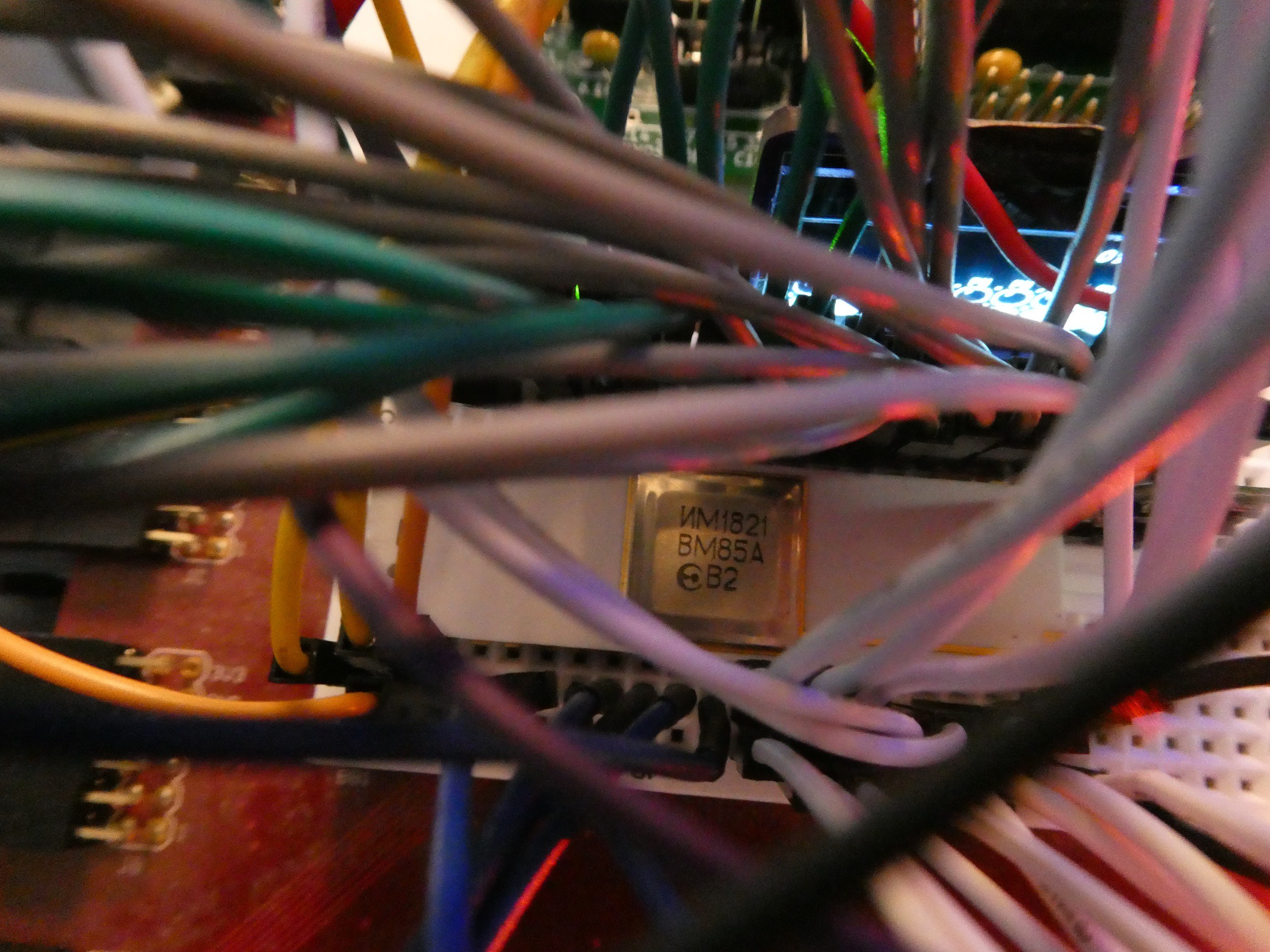

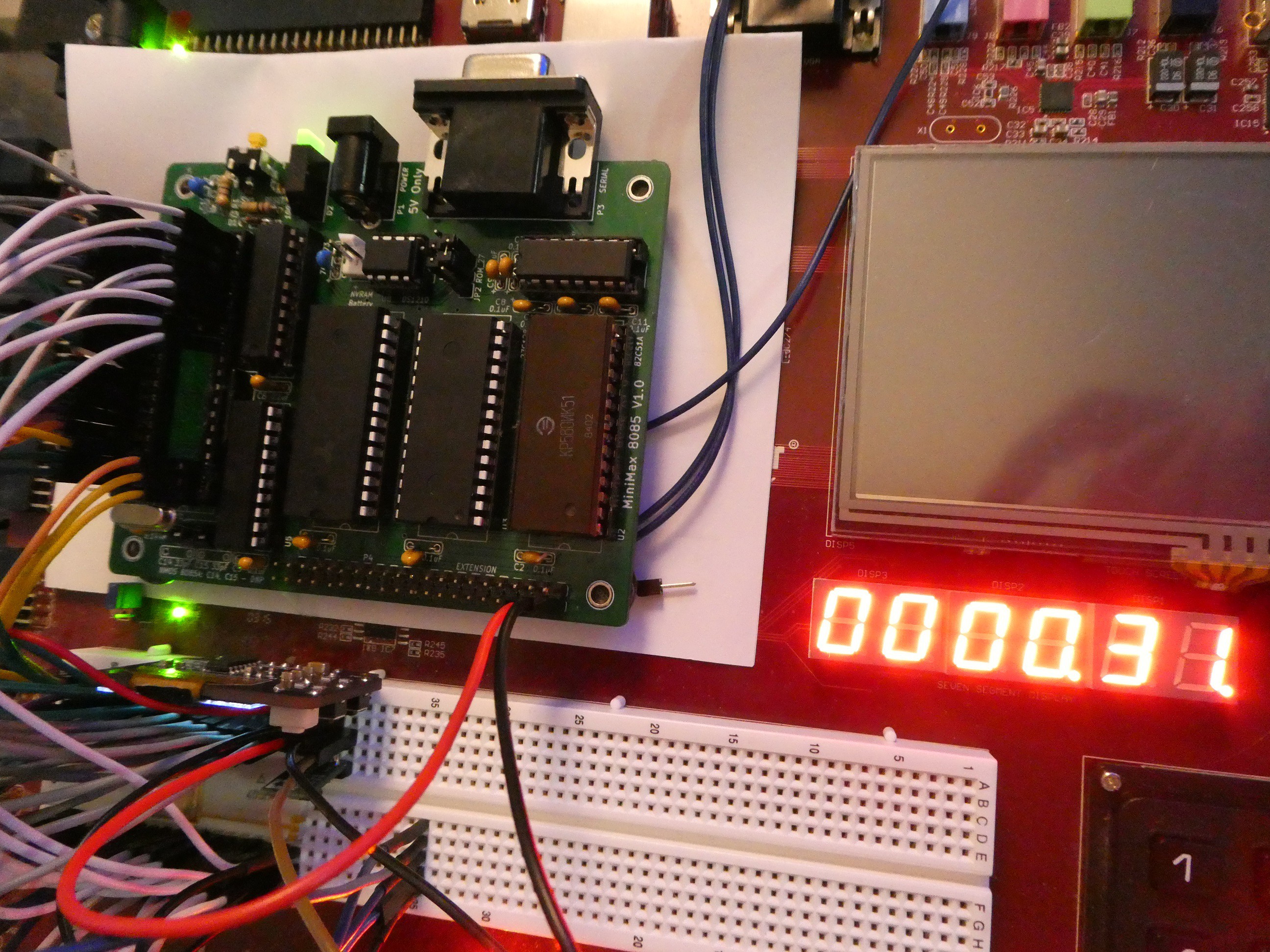

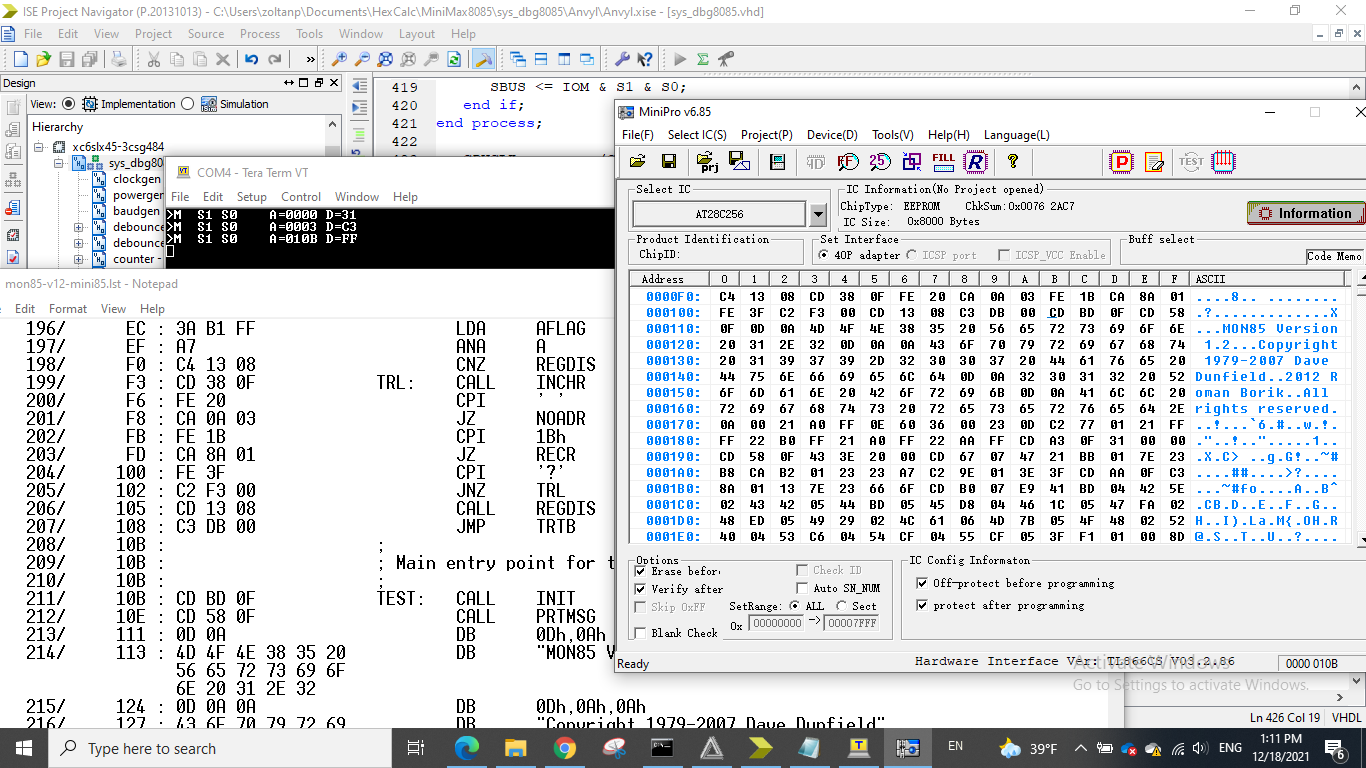

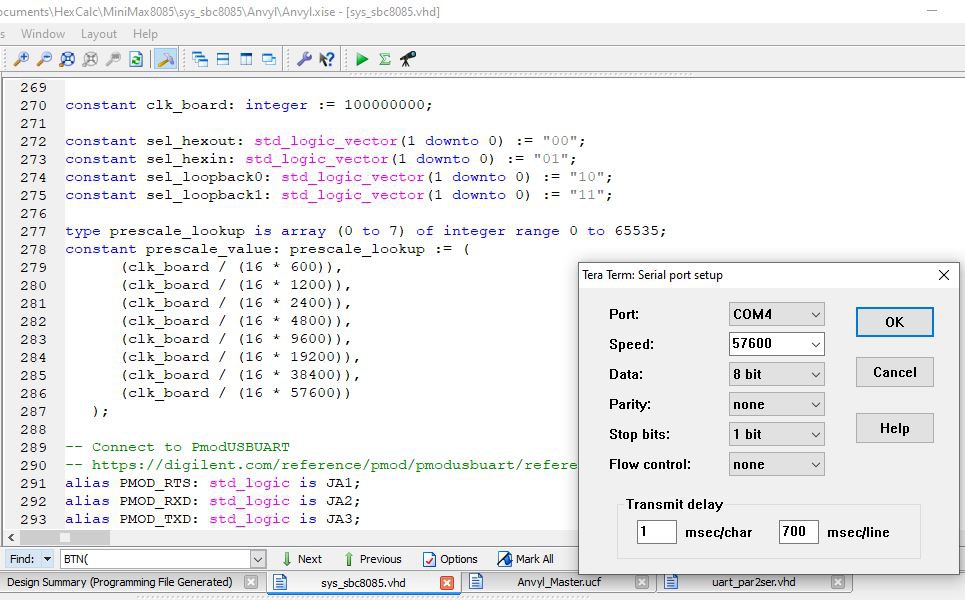

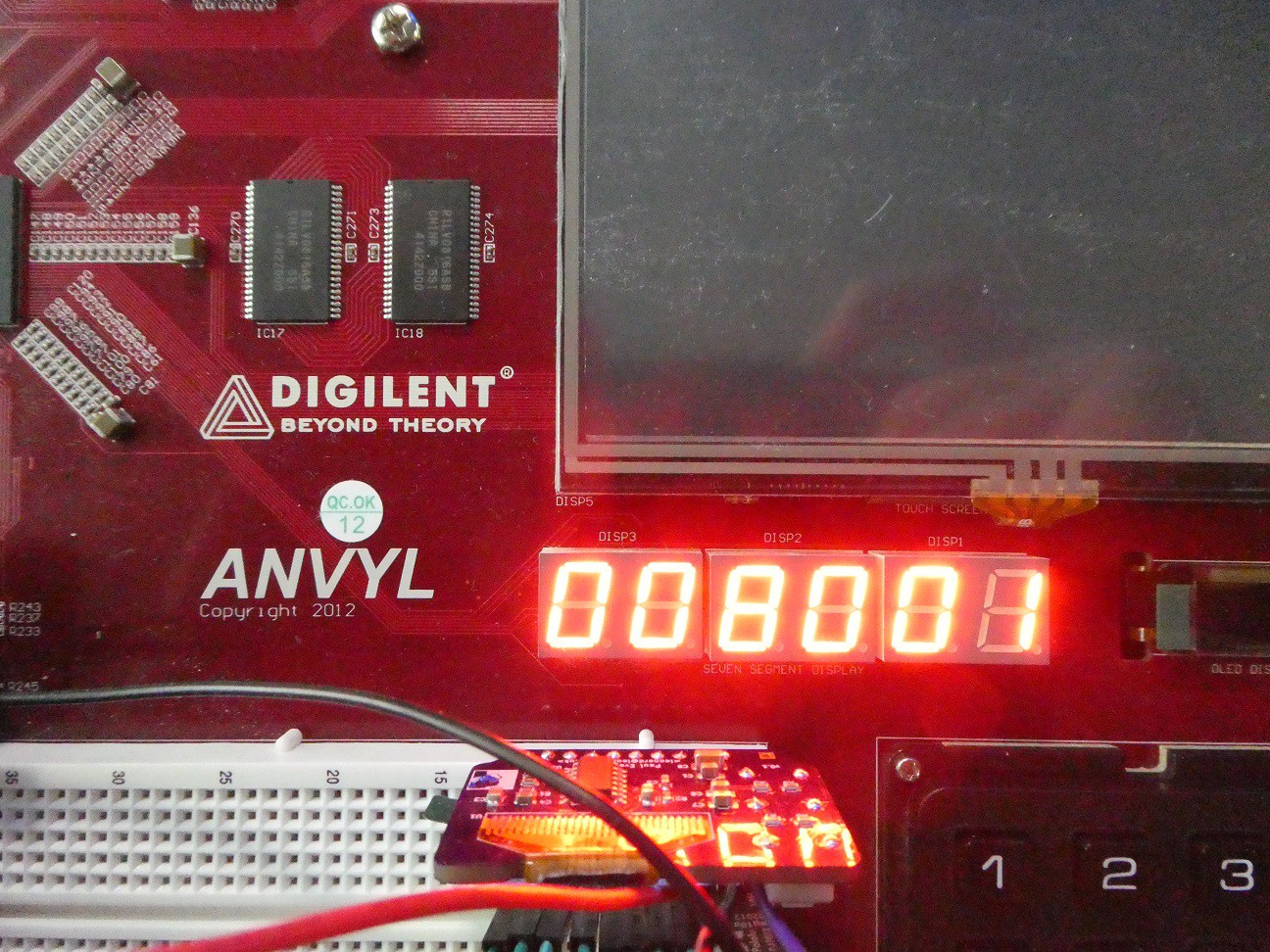

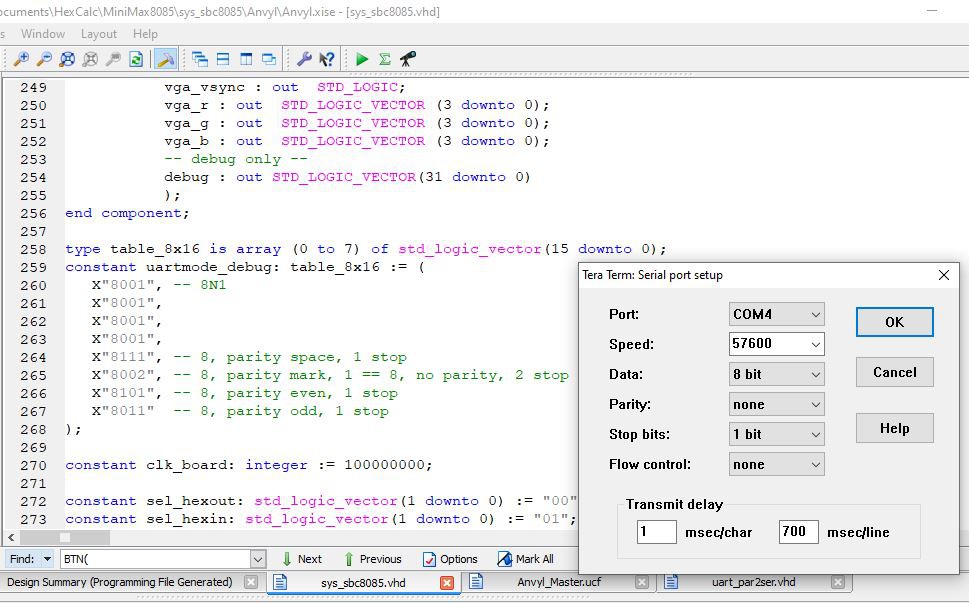

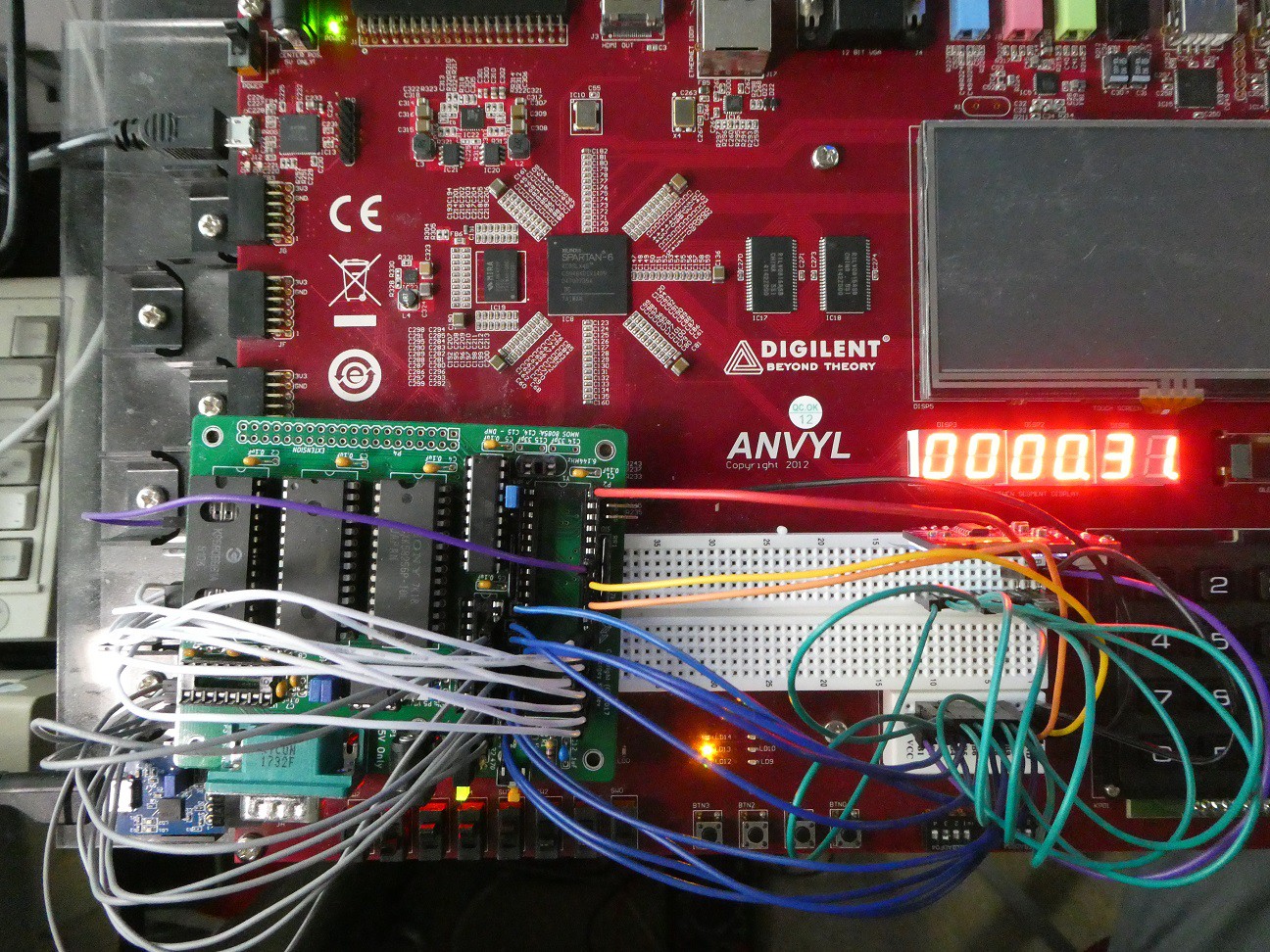

Turns out, with some breadboards, wiring, and bringing the Intel HEX component buses outside from FPGA into the physical world, the same components can be reused for a custom and handy testing tool.

This testing allows to check:

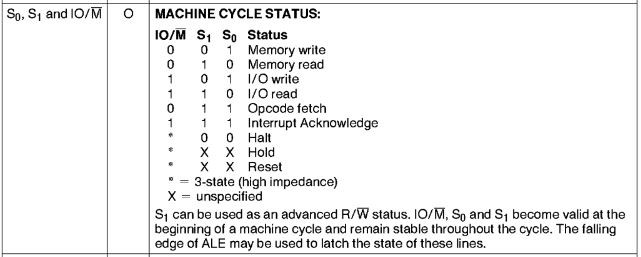

- Address, data, some control (R/W) buses

- (EP)ROM/RAM if populated (for expected content or read / write / re-read)

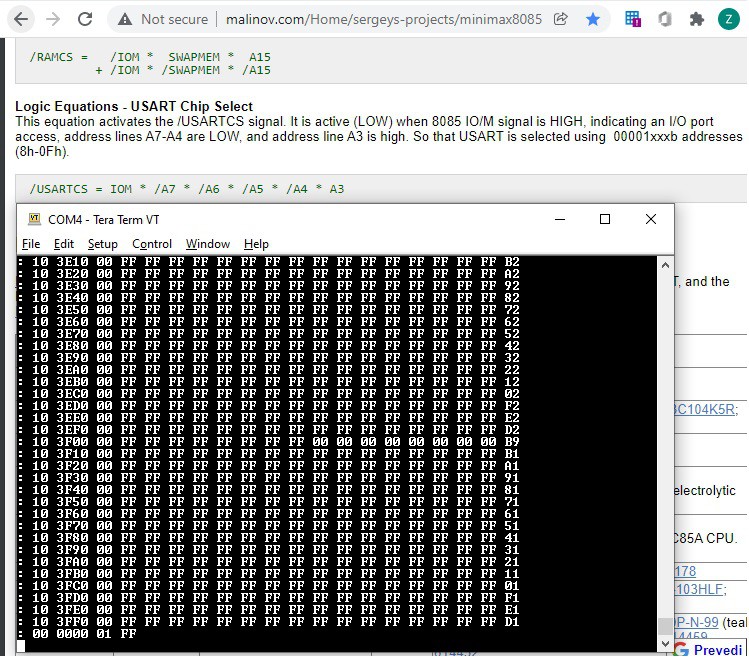

- Address decode logic (e.g. mapping of ROM/RAM, repeats due to partial decode etc.)

Note that boards / computers tested this way do not need to be populated fully with ICs or other components, so it is possible to check "dead" or "not yet alive" boards too.

There are two possibilities:

- CPU is not on the board, "insert" the wires into CPU socket (poor man's in-circuit emulator)

- CPU is on the board, but there is bus access that allows DMA takeover (e.g. BUSREQ/BUSACK in Z80-type buses)

What cannot be readily tested using this approach:

- Non-memory oriented bus signals (e.g. clocks, interrupts etc.)

- I/O (memory mapped) - there can be indication that it "kinda works" as those spaces will be read as whatever default the I/O device returns, and in case of write in some simple case (e.g. write latch connected to some LEDs or relays) it may work.

- I/O (separate) - with extra signal I/O space can be "forced" to appear as memory space and then it can be figured out if the data returned makes sense or not (example given below)

zpekic

zpekic

Erik Piehl

Erik Piehl

teardownit

teardownit