This circuit tested my sanity.

.

.

.

The counter will take clock B as an input (slow clock). With each clock pulse the contents of the counter need to be decremented by 1. There will be 4, 4 bit registers that contain the base 10 value for each seven segment digit. Meaning if the counter is displaying 2355, the registers should contain the following [0010/0011/0101/0101]. After the next clock pulse, the contents will be decremented and registers will now contain [0010/0011/0101/0100].

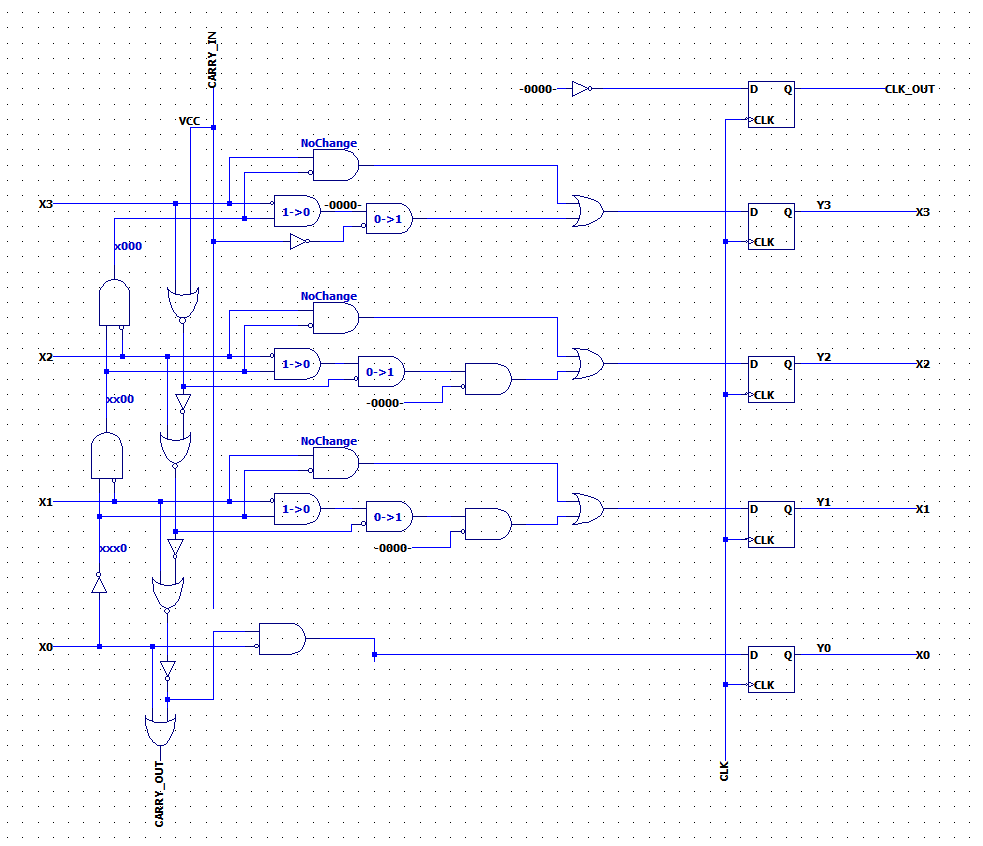

Having avoided for the most part neglected digital logic since second year, this circuit by far was the most difficult to configure. There’s likely some way to condense this circuit, however, due to a bit of a time crunch no further improvements will be made. The final counter circuit is shown below.

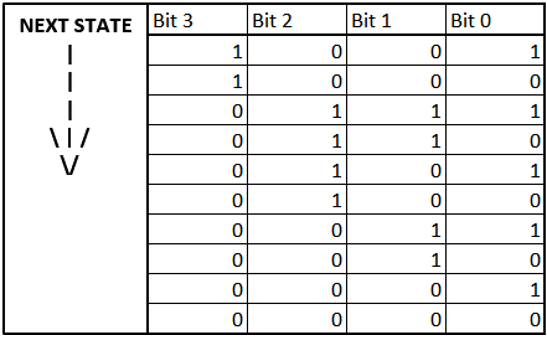

The logic for each bit is practically mirrors (excluding X0), so the logic will be explained for X3 and the reader should be able to make sense of the subsequent logic. It may be helpful to refer this table.

For a transition from 1 to 0 requires that all lower bits are 0. To transition from 0 to 1 requires that all lower bits are 0 and there is a 1 in any of the upper bits. For the highest bit X3, this is pulled from the next BCD block using CARRY_IN. Similarly, when bit X3 transitions from 0 to 1 the next BCD block is given a clock pulse via CLOCK_OUT. Note that CARRY_IN is used to set the output back to 1001 (9).

One major flaw of this circuit is that the initial state is unknown. As a result the 7SEG will display garbage until the user cycles the clock (or the clock is allowed to tick away) into a valid range (digit 0->9). Once in its valid range the counter will be locked in the range of 9->0. If a revision of this circuit is made I will address this bug (this project has already ballooned as is).

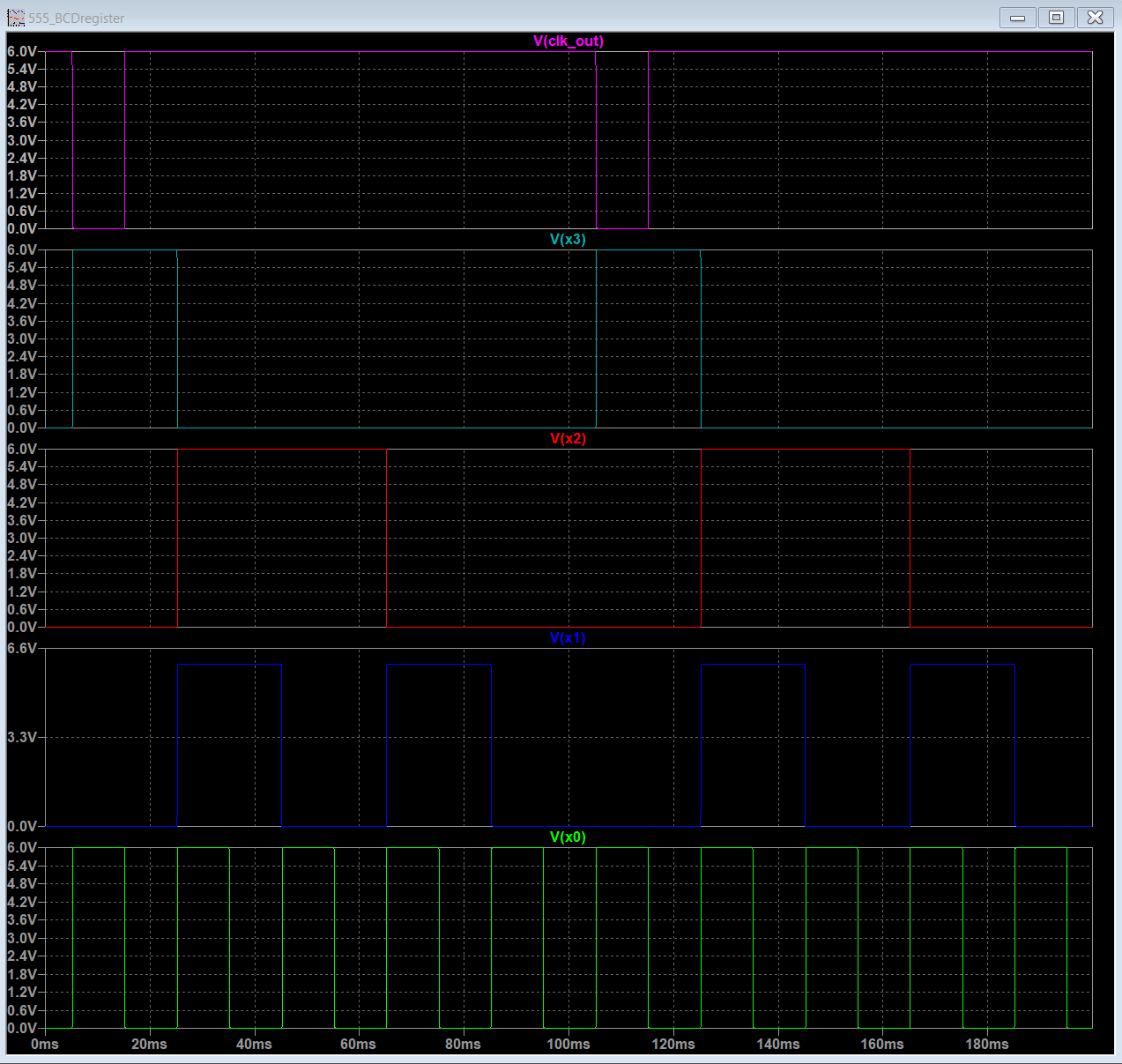

Here are the simulation results with CARRY_IN held high.

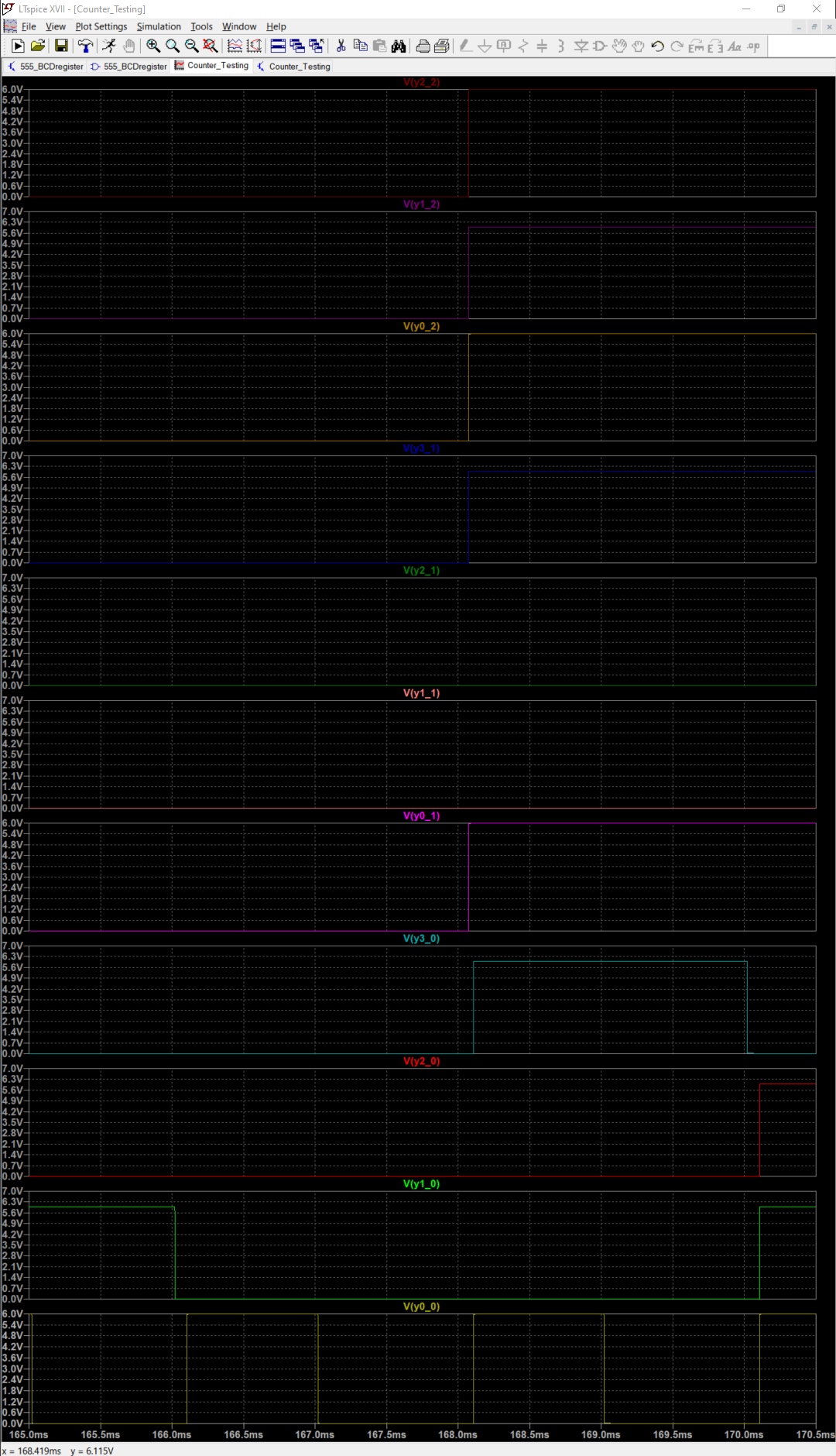

Heres a capture of several cascaded BCD counters. I've zoomed in on the 0->9 transistion to ensure that the counter loops to 1001 and not 1111.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.