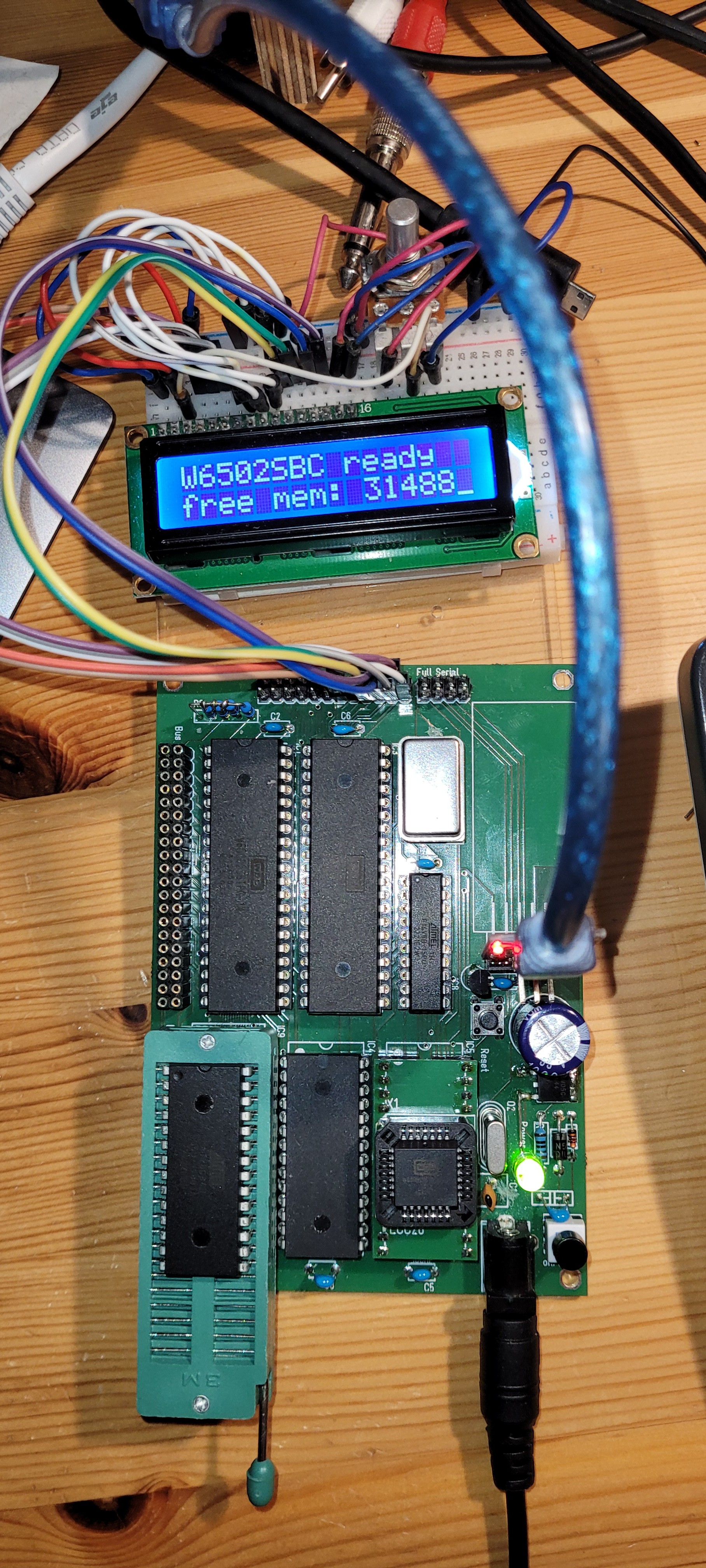

An old topic has been bothering me for a long time. Assembler and 6502. My C64 has been mothballed for a long time, the VC20 is selling. Nevertheless, I find the 6502 very interesting in terms of assembly language. What you could do with 1MHz and 64kb RAM. This year (2022) the time had come. I decided to build a 6502 SBC. There are many, many posts and suggestions on the Internet about this. Unfortunately, there is no version that you could easily rebuild and that meets my expectations of a 6502 workbench computer. Here are my requirements in brief:

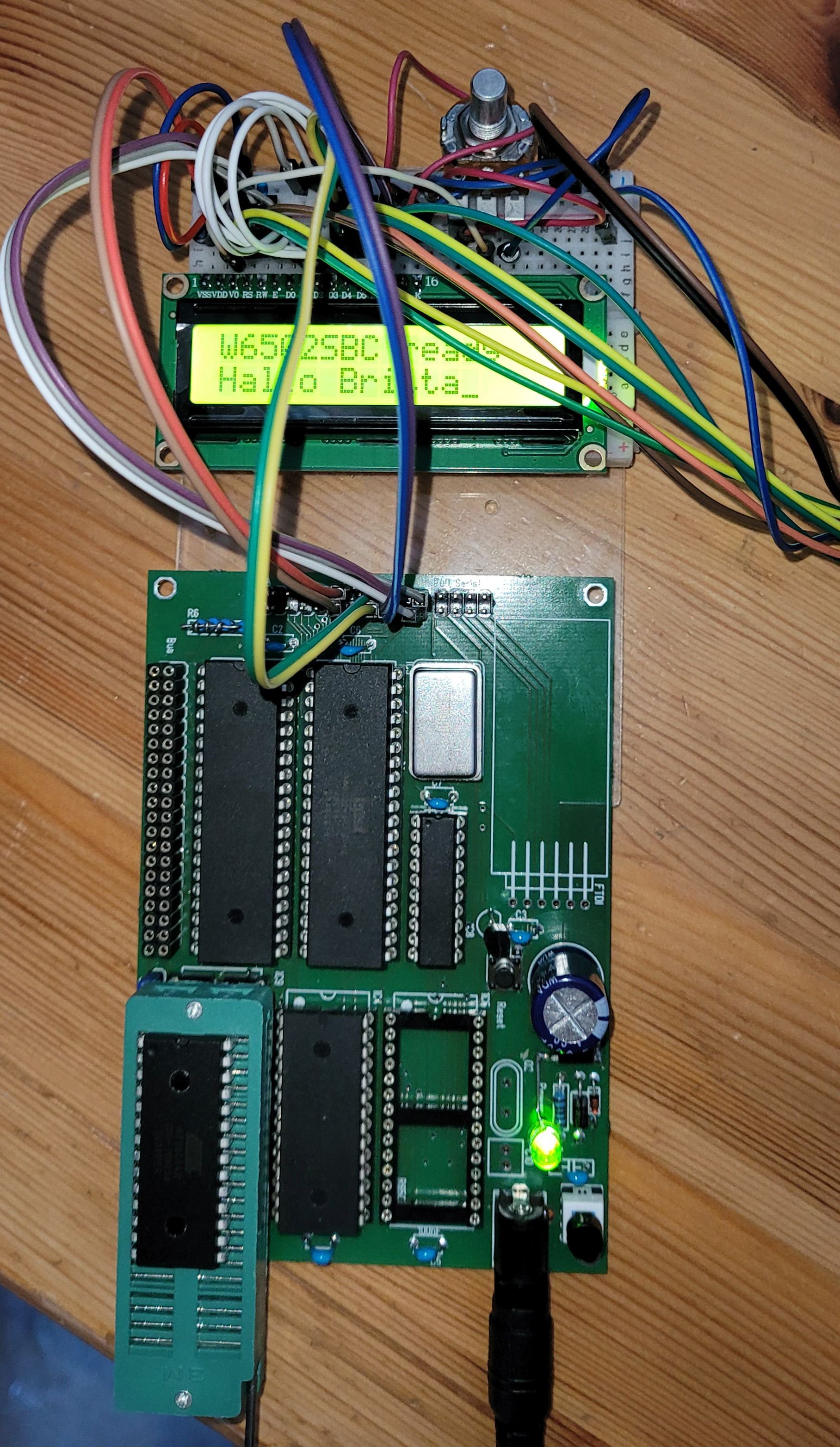

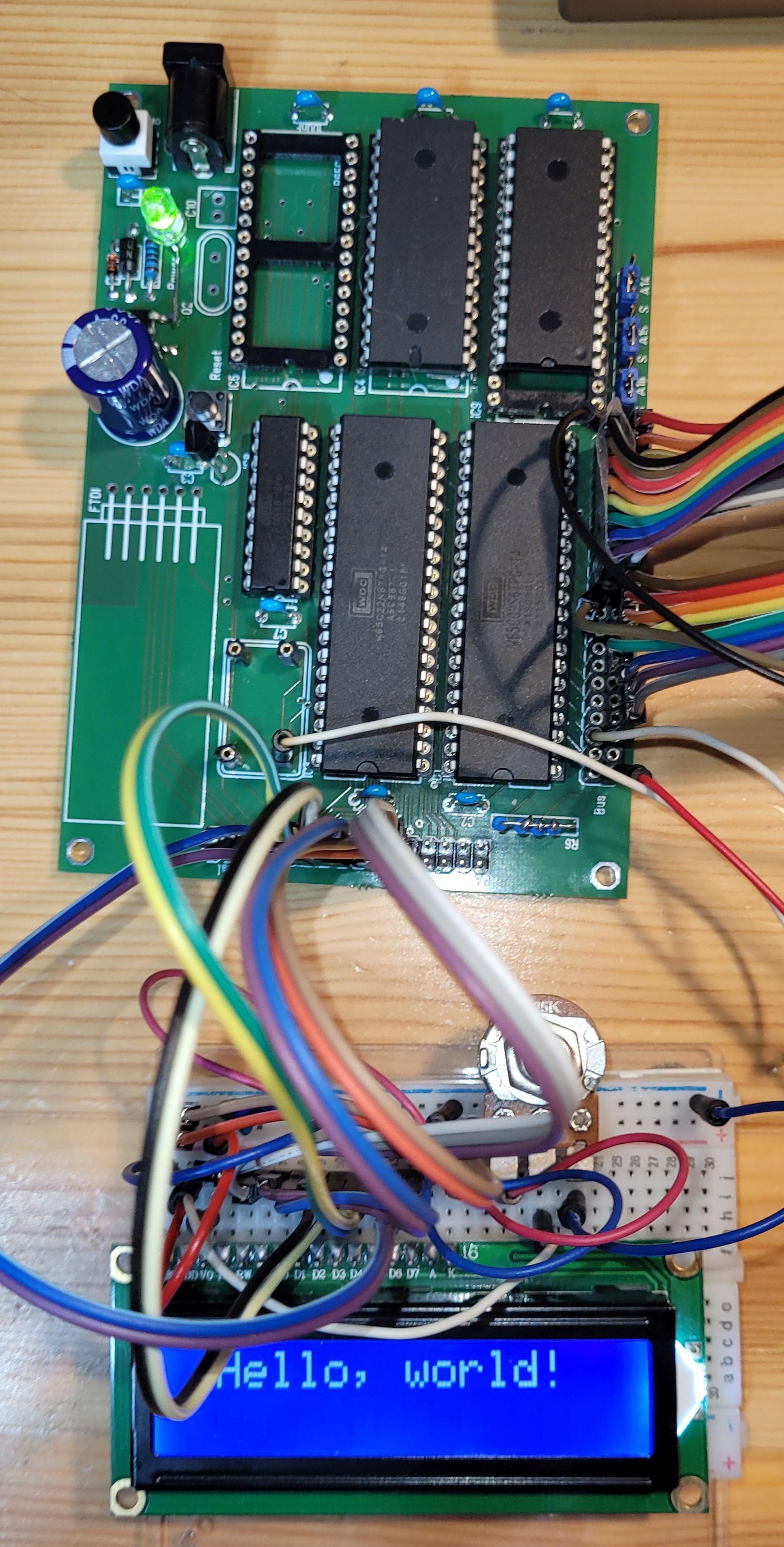

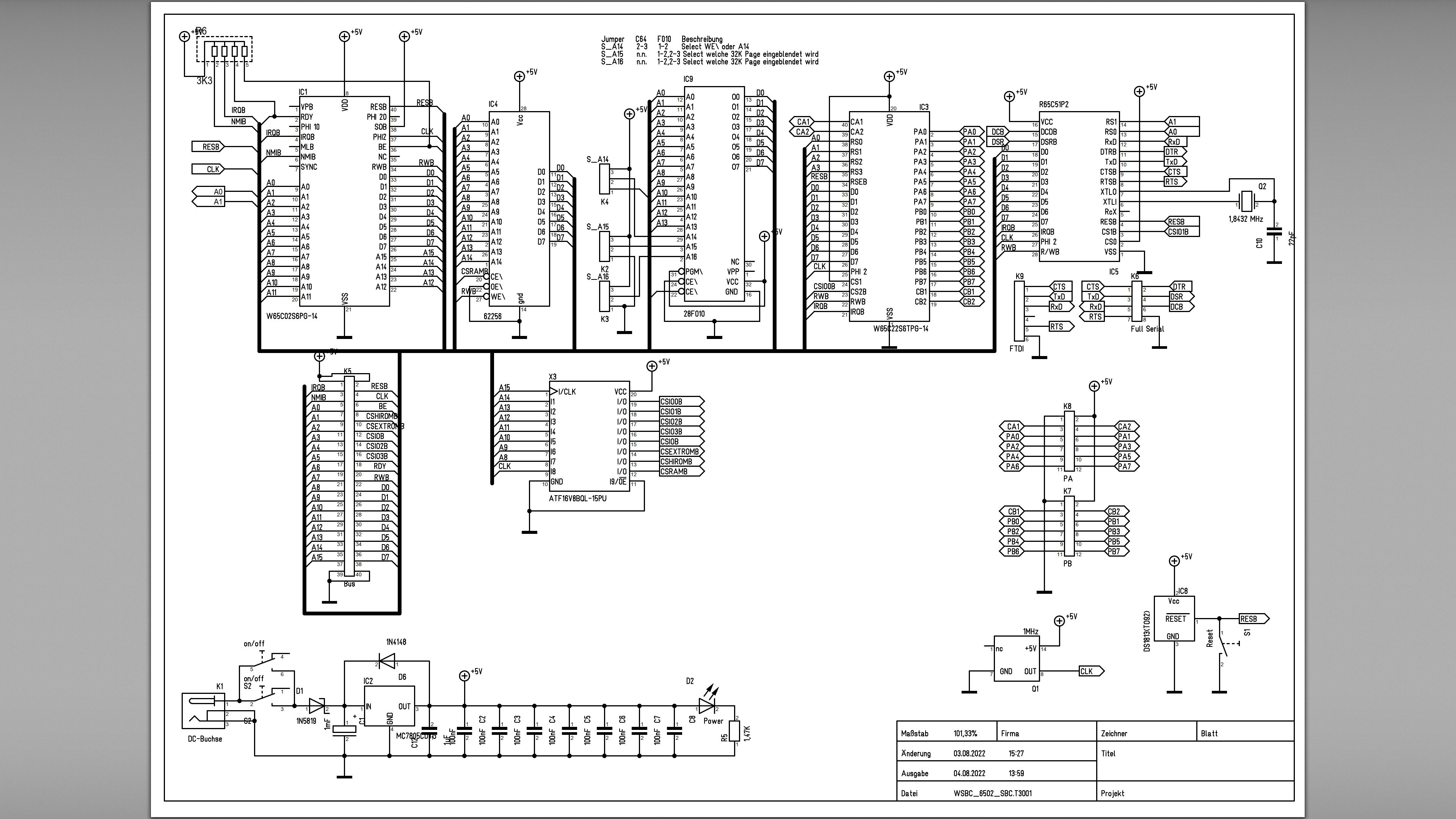

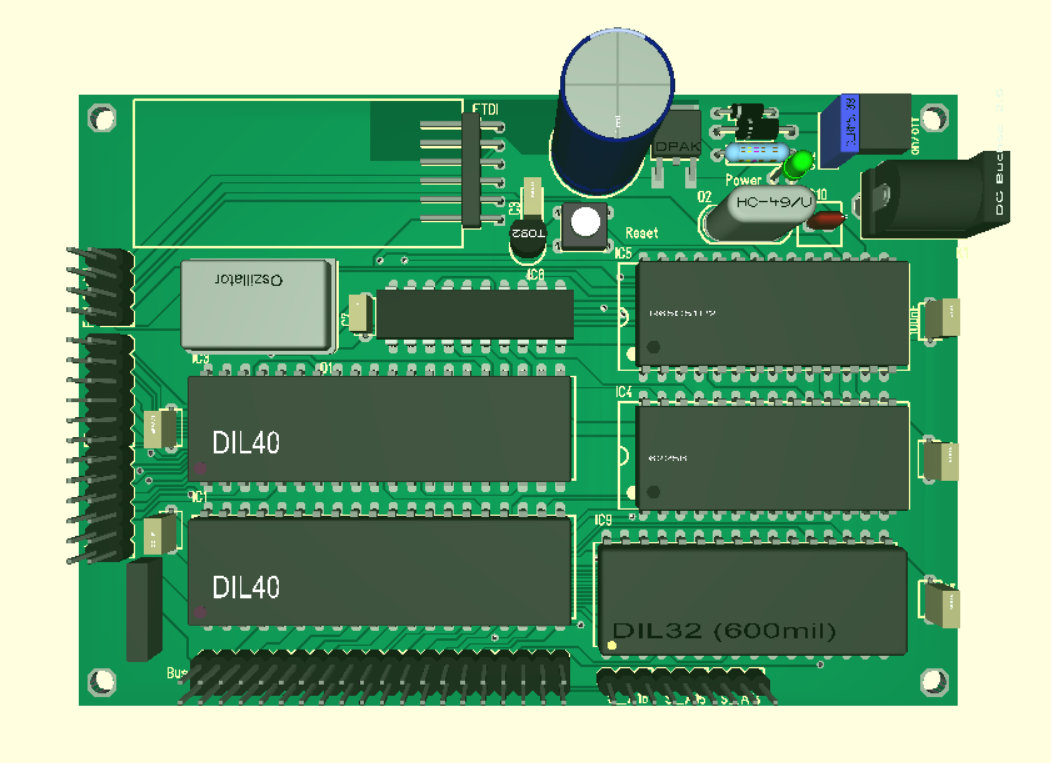

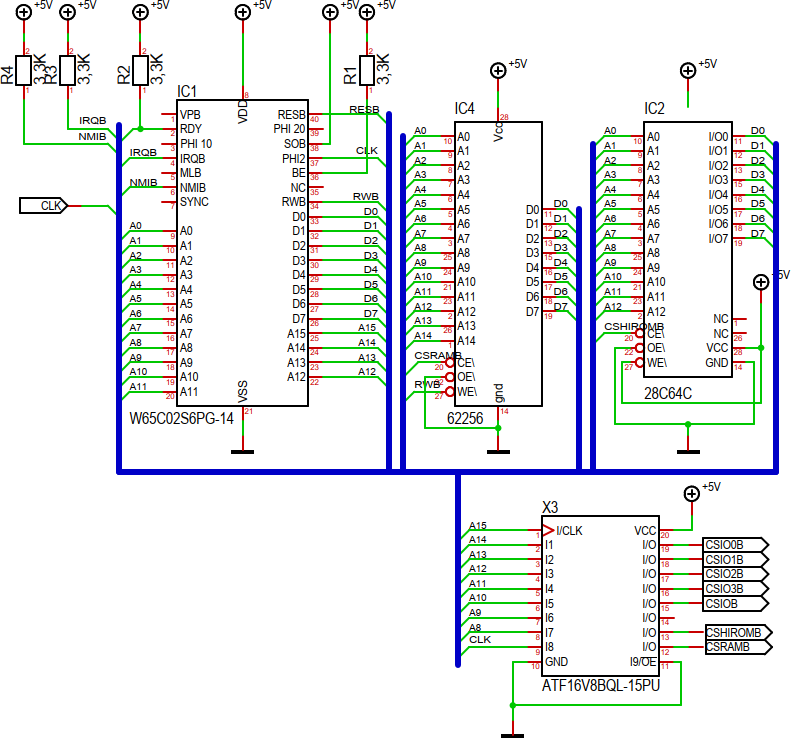

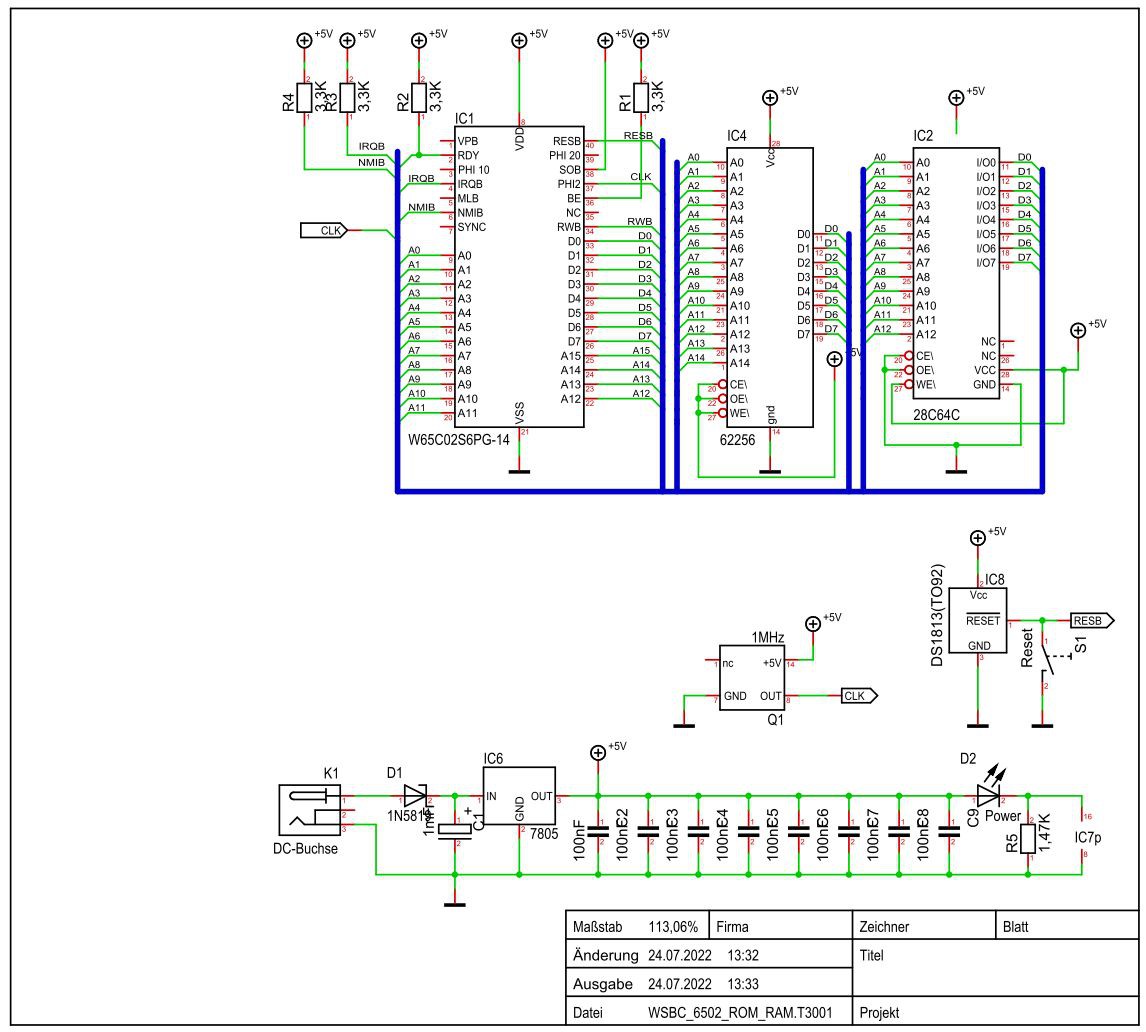

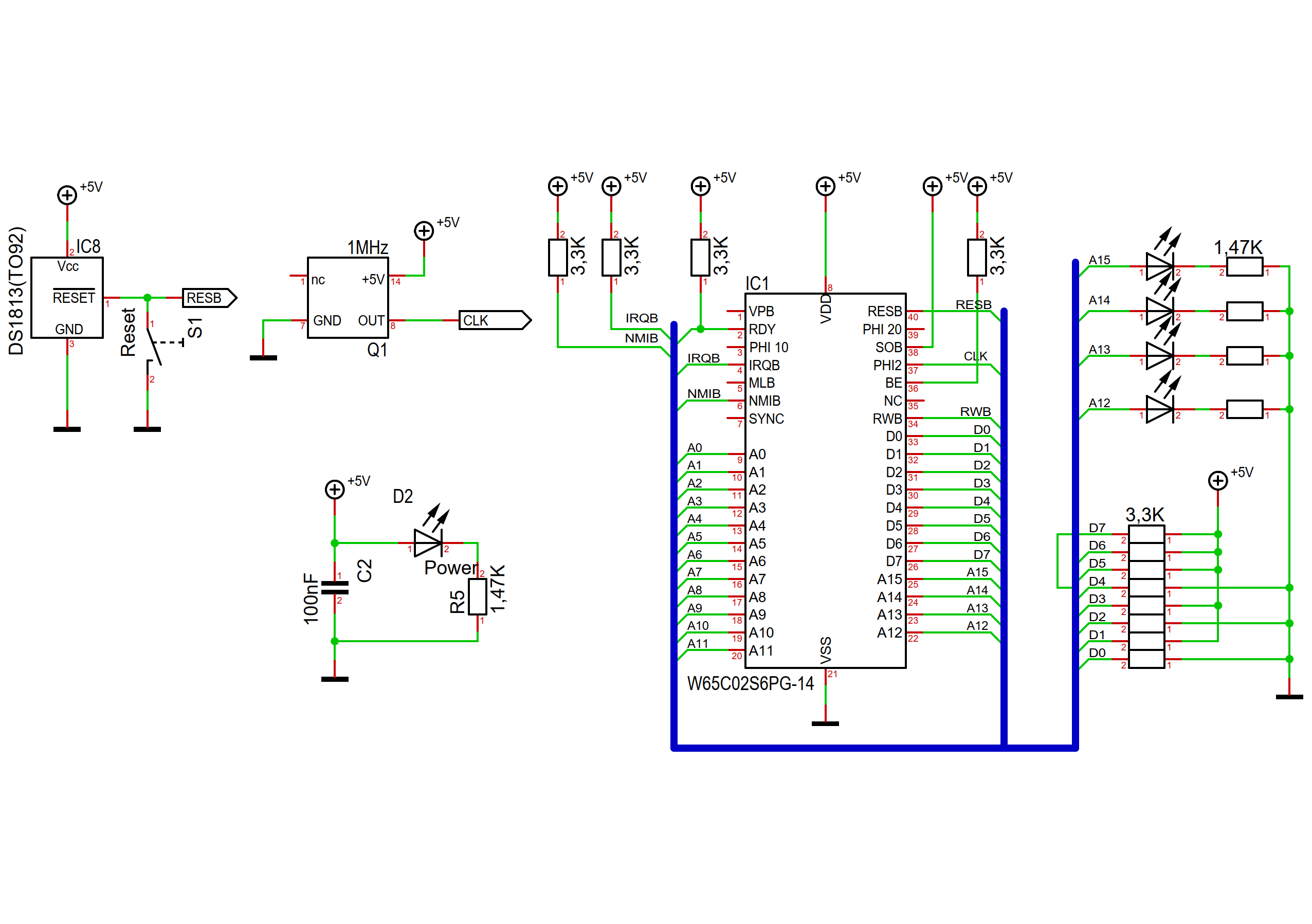

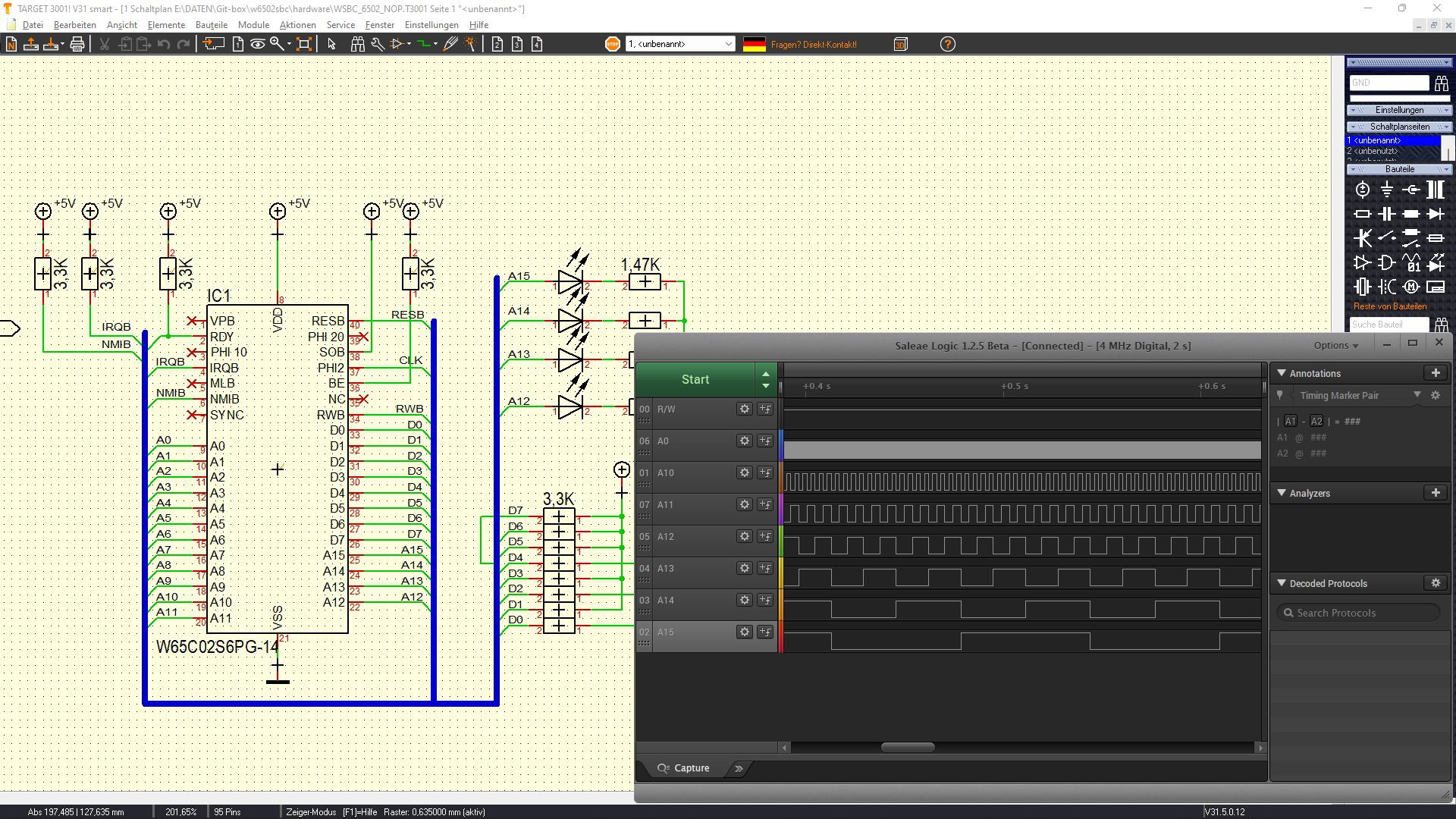

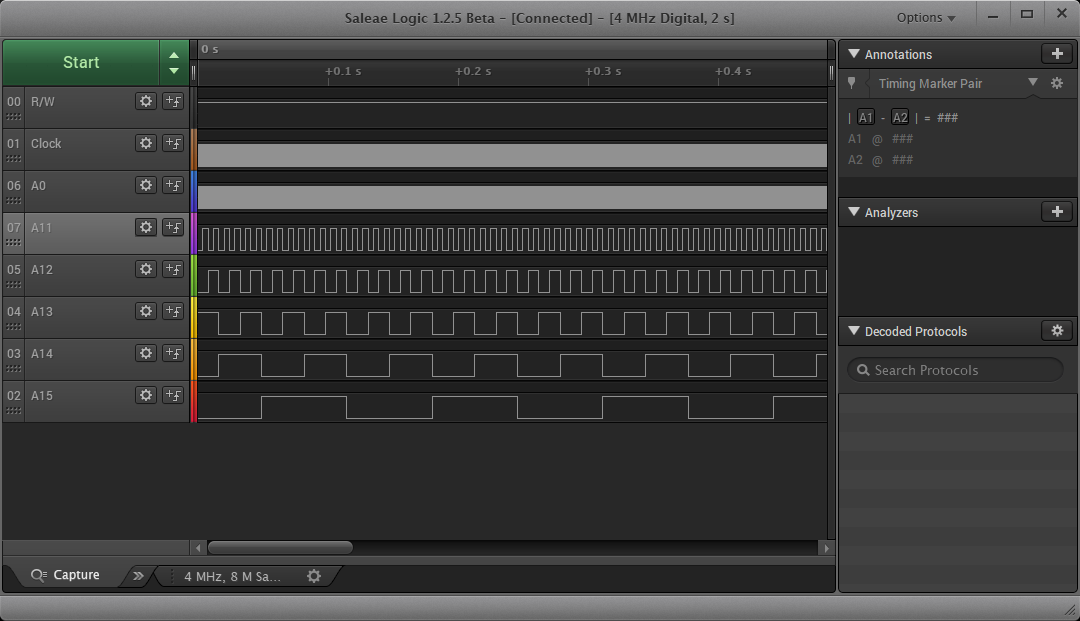

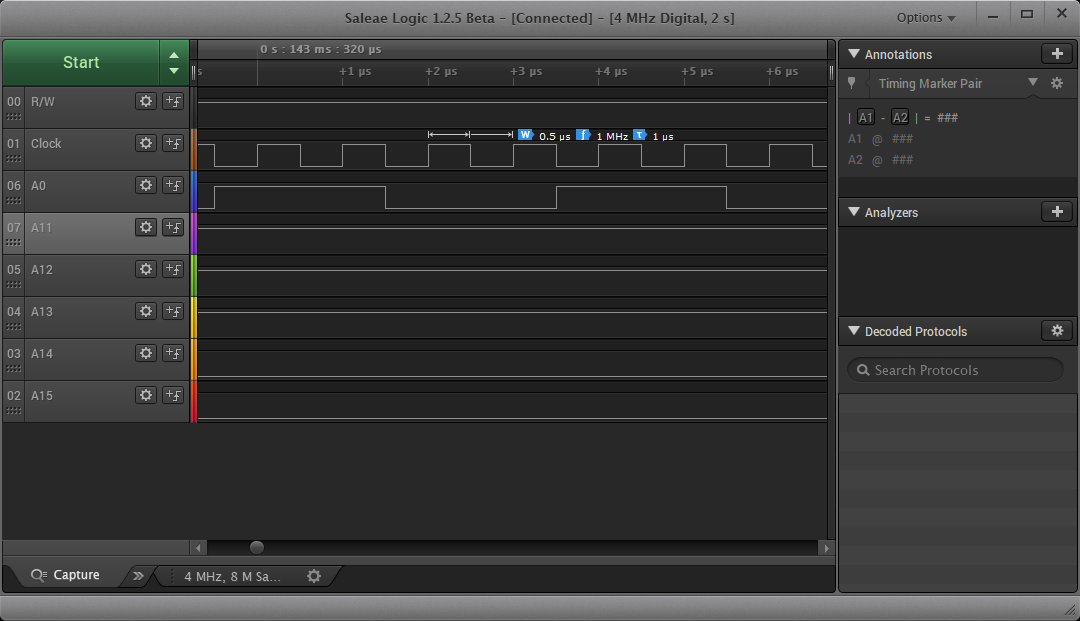

- WDC65C02 CPU with 4MHz (clock can be switched by program)

- WDC65C22 VIA with 4MHz, possibly 2 of them

- 6551 ASIC for the serial port (R65C51)

- 32Kb or 64KB SRAM (both were available)

- EEPROM or Flash as Kernal/Basic ROM

- NMI and IRQ assignable

- Variable memory allocation, possibly also modifiable from the outside

- Plug-in card system or system bus, preferably with corner edge connectors, as in the C64, VC20, a suitable backplane would be nice

- no video, audio or anything

- SPI over 6522, so you can connect a display/keyboard

- CPLD for something

- opt. LC display

I started on July 22. Initially with orders from Mouser and Reichelt.

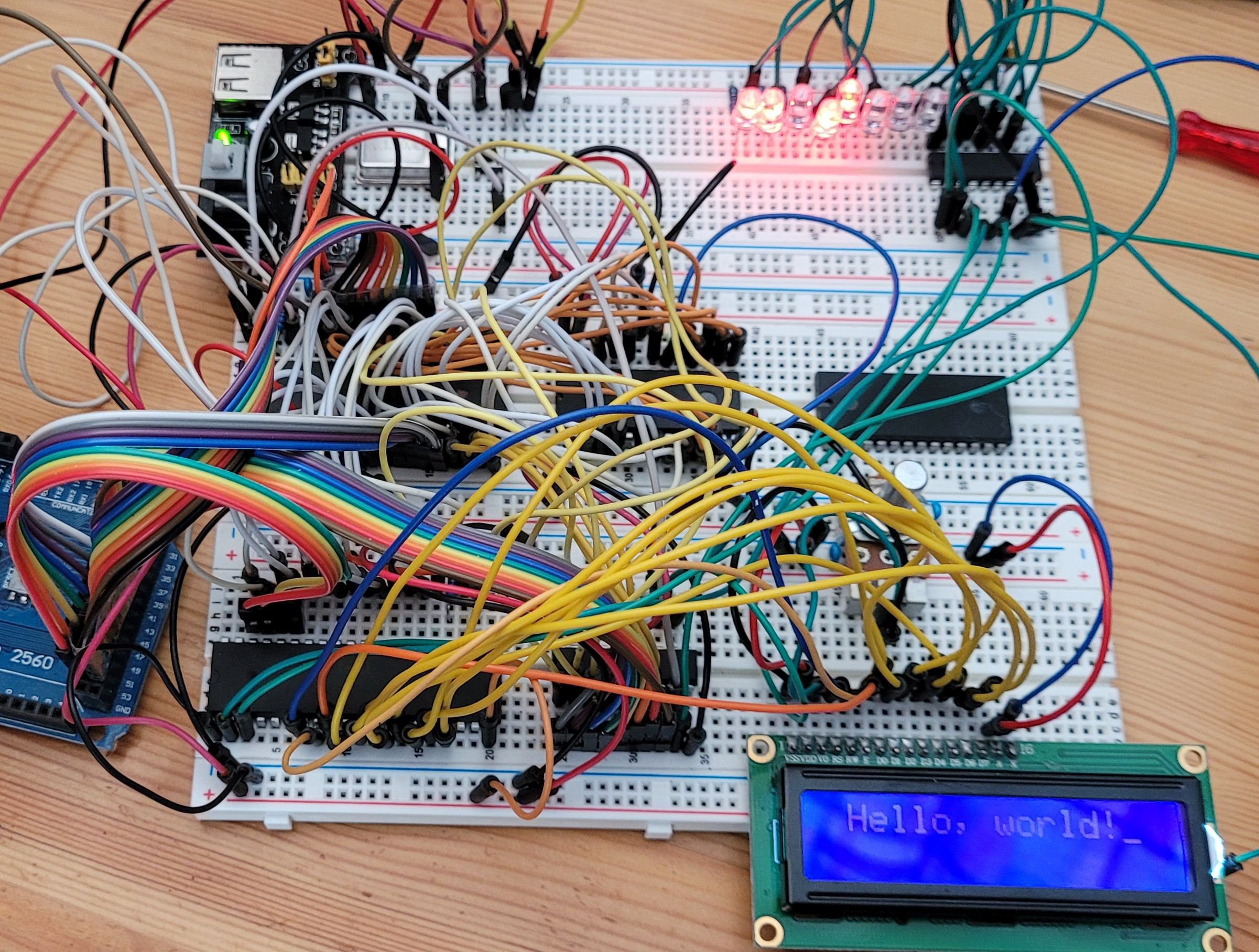

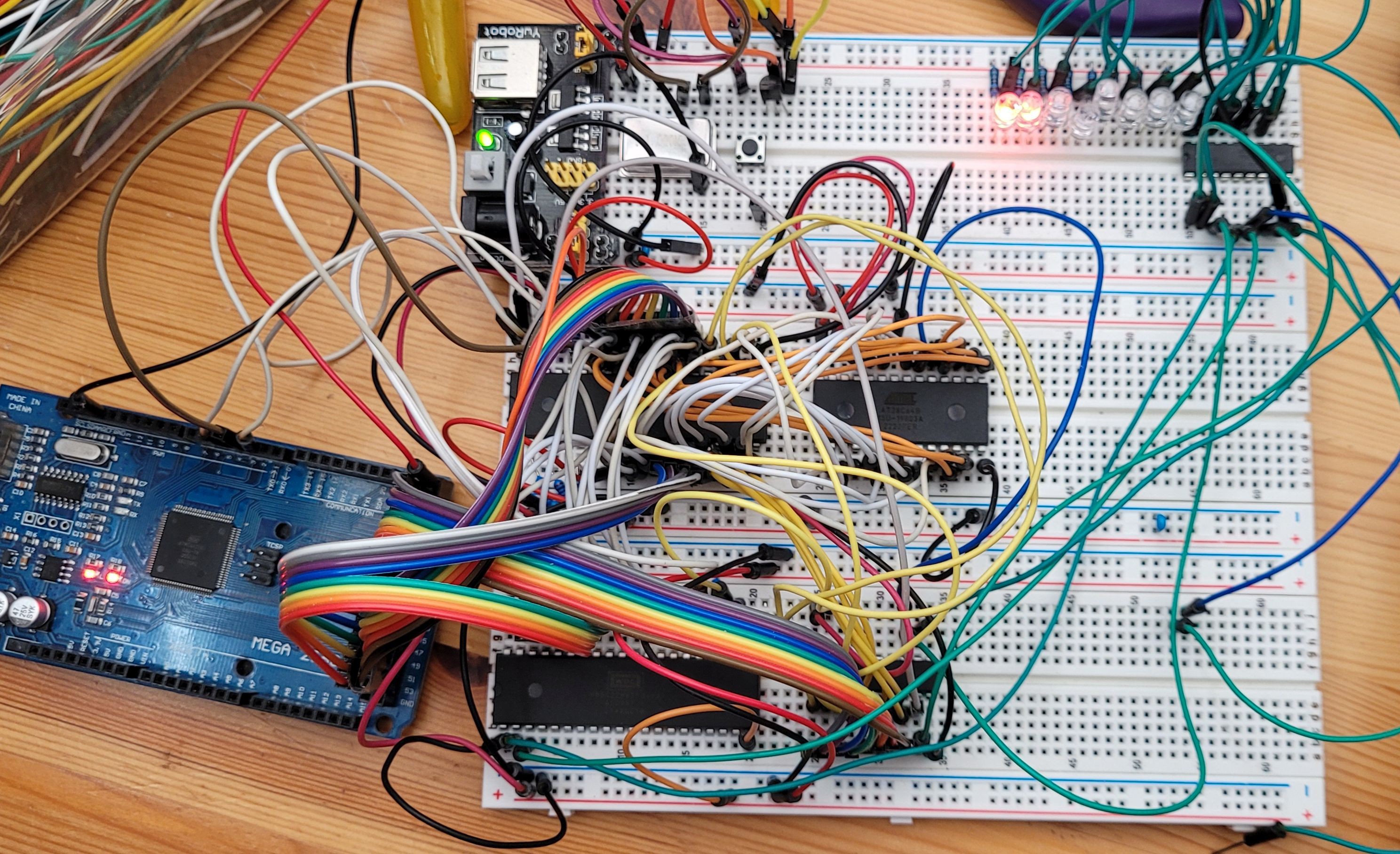

Follow the steps to learn:

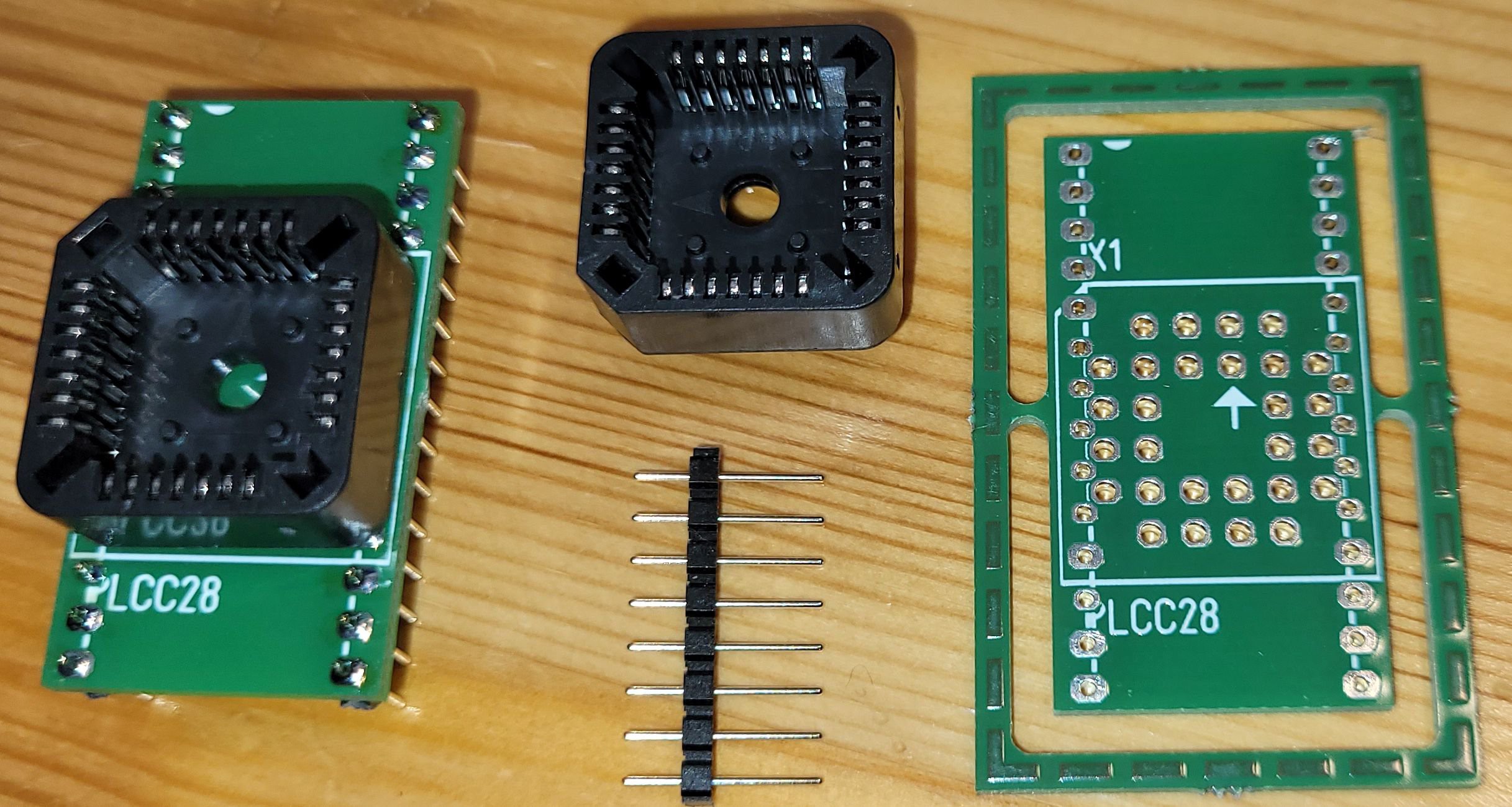

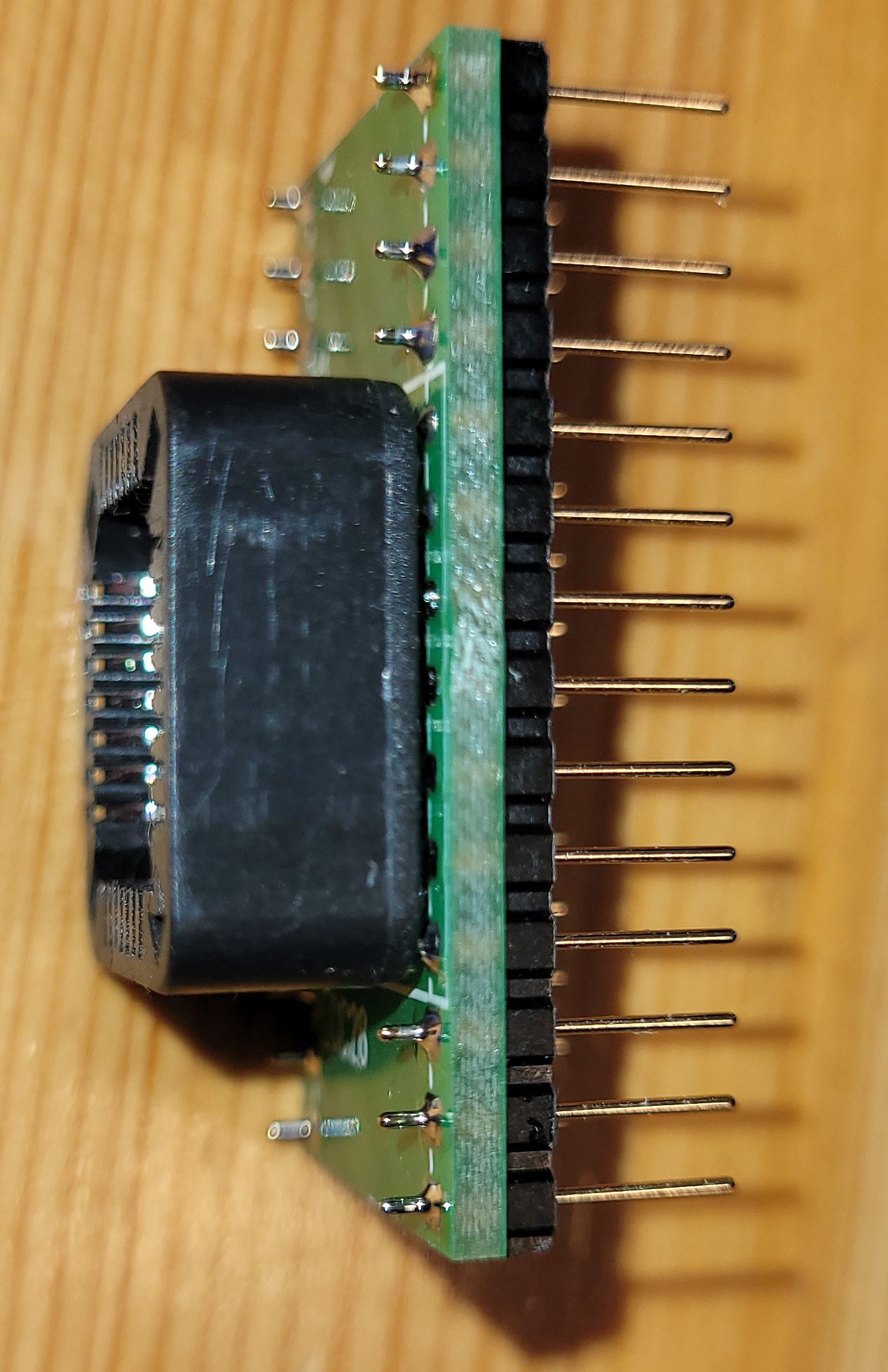

- CLPD: I needed a programming adapter for this (my choice was a TL866II+)

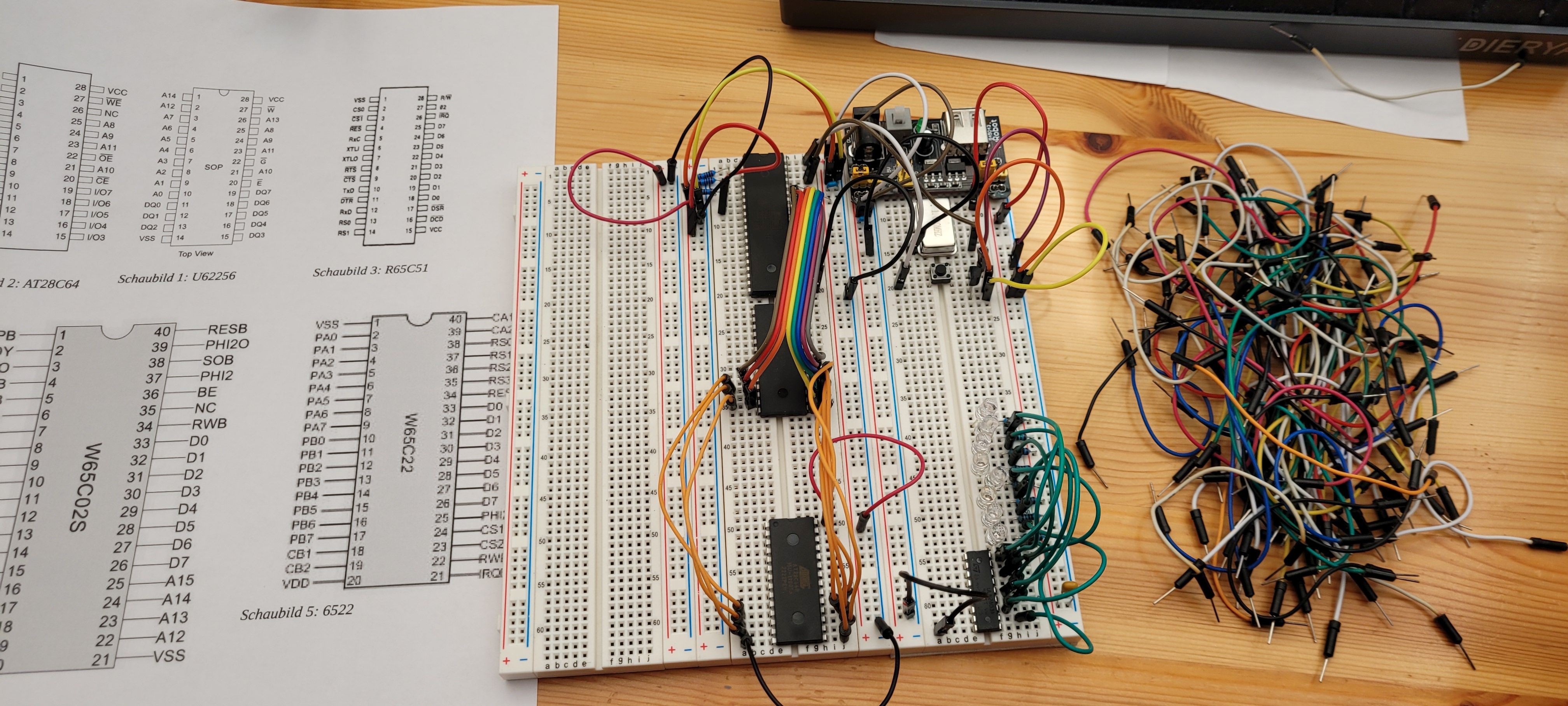

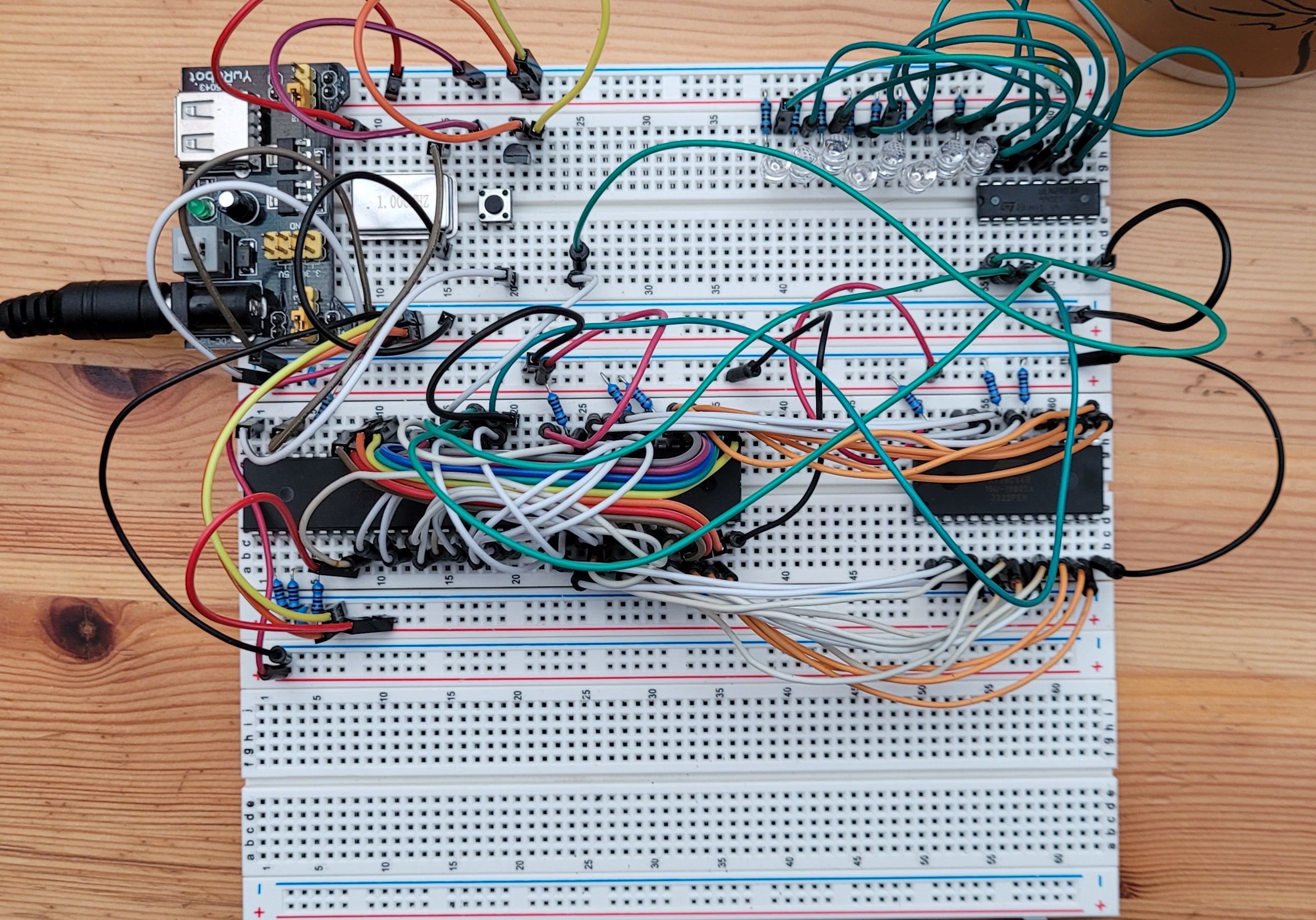

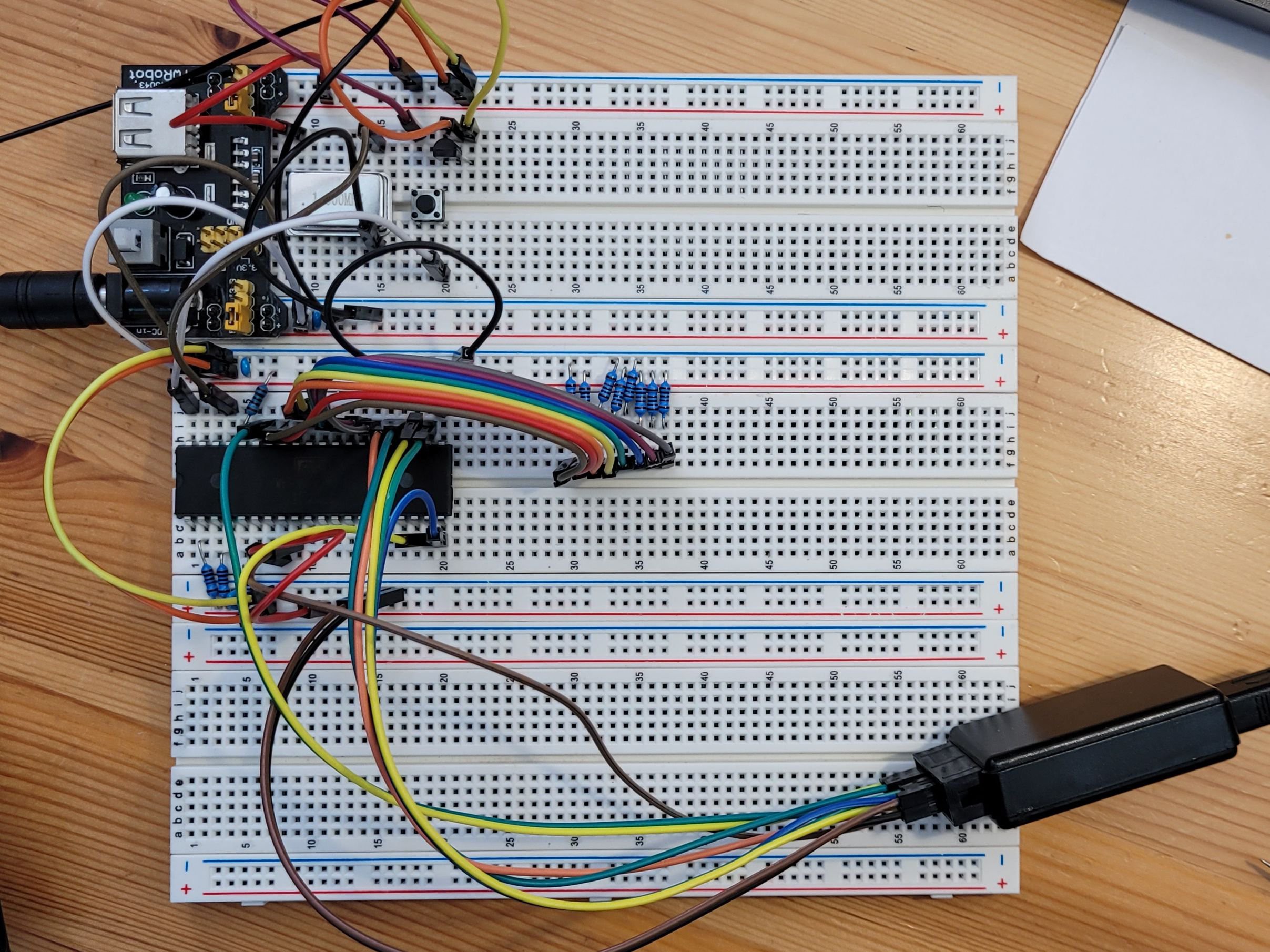

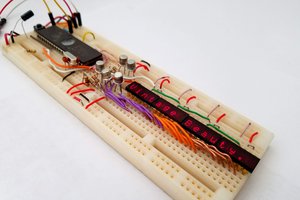

- build a simple system on breadboard with 1MHz

- Implement Wozmon

- ...

At the end of the first section there should be a CPU plug-in card with a working 6502 system. Incl. BASIC via terminal. VTL-2 and Basl (my own small language) would be considered as further languages.

More information and project logs are here:

https://github.com/willie68/w6502sbc

Wilfried Klaas

Wilfried Klaas

rawe

rawe

Ethan Durrant

Ethan Durrant

Arduino KIT

Arduino KIT

Mederic

Mederic

Did you have a look at my Sym-1? The 8kb Assembler is quite comprehensive for the memory allocated to it. The real revelations come from Hans Otten's Retro Site. http://retro.hansotten.nl/6502-sbc/synertek-sym-ktm/sym-1/

And all the manuals he has documented. The 6502 Assembler is in there. The Sym-1 RAE is there along with the ROM images too http://retro.hansotten.nl/6502-sbc/synertek-sym-ktm/sym-1/

I hope your project is going well, best wishes, Rob