Subtraction

I have had a bit of a problem getting my head around subtraction and the borrow/carry flag. With some CPUs (such as the 6502) the carry flag is set and when underflow occurs then the carry flag is cleared. This works of course but makes JNC is not so useful.

The 8086 works the other way. The carry flag is cleared and when underflow occurs the the carry flag is set. Since the 8085 and 8086 were my first microprocessors, I will go with this system, and JNC works better here.

For the time being I am going to "jumper out" ADC and SBB, for ADD and SUB, as these instructions are more trouble then they are worth, at the moment.

I have used the most significant bit of the page register as an OPCODE flag.

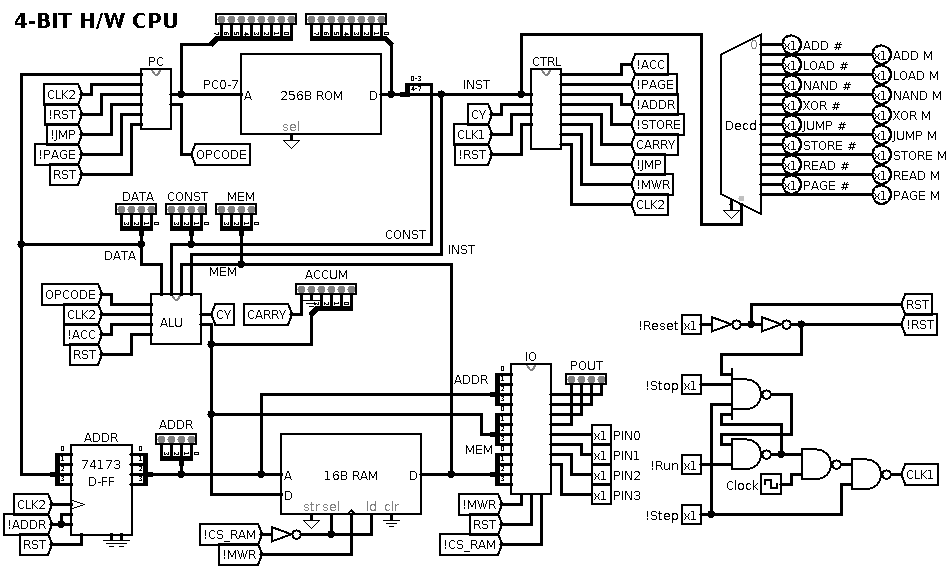

Here is the top level view:

Here is the PC:

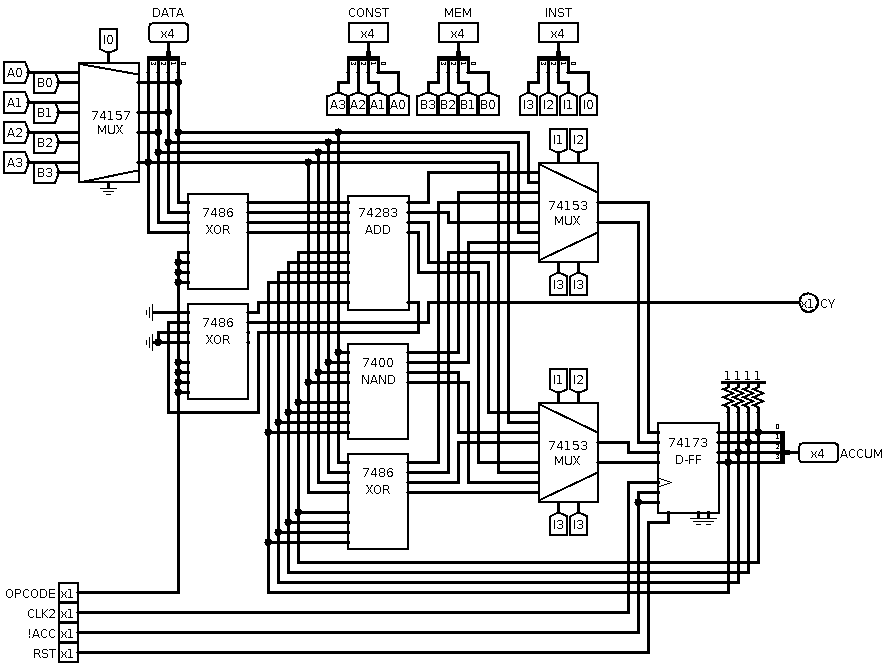

And the ALU:

The PAGE op code E0 sets ADD and op code E8 set SUB.

Note E0 00 clears carry while E8 00 sets carry.

It is clear we can add other instructions to the ALU if desired.

Here is some code to count up and then count down. JNC is tripped on overflow/underflow:

E0 Set ADD 00 Clear Carry 20 Clear ACC AF Output ACC A0 Store to Mem[0] 01 ADD 1 83 JNC 3 00 Clear Carry E8 Set SUB 2F Set ACC to F AF Output ACC A0 Store to Mem[0] 01 SUB 1 8A JNC A E0 Set ADD 00 Clear Carry 82 JMP 2

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.