I owned an Amiga 1200 "back in the day" with a 40 MHz Motorola 68030 and 34 MB of RAM. I grew up using this computer and began learning to program on it. Now as a professional programmer I regret not having had the chance to apply the skills I have now to that old machine. However I do work with people who made games from that generation. They've told me the cool things they made these machines do, and the techniques they used.

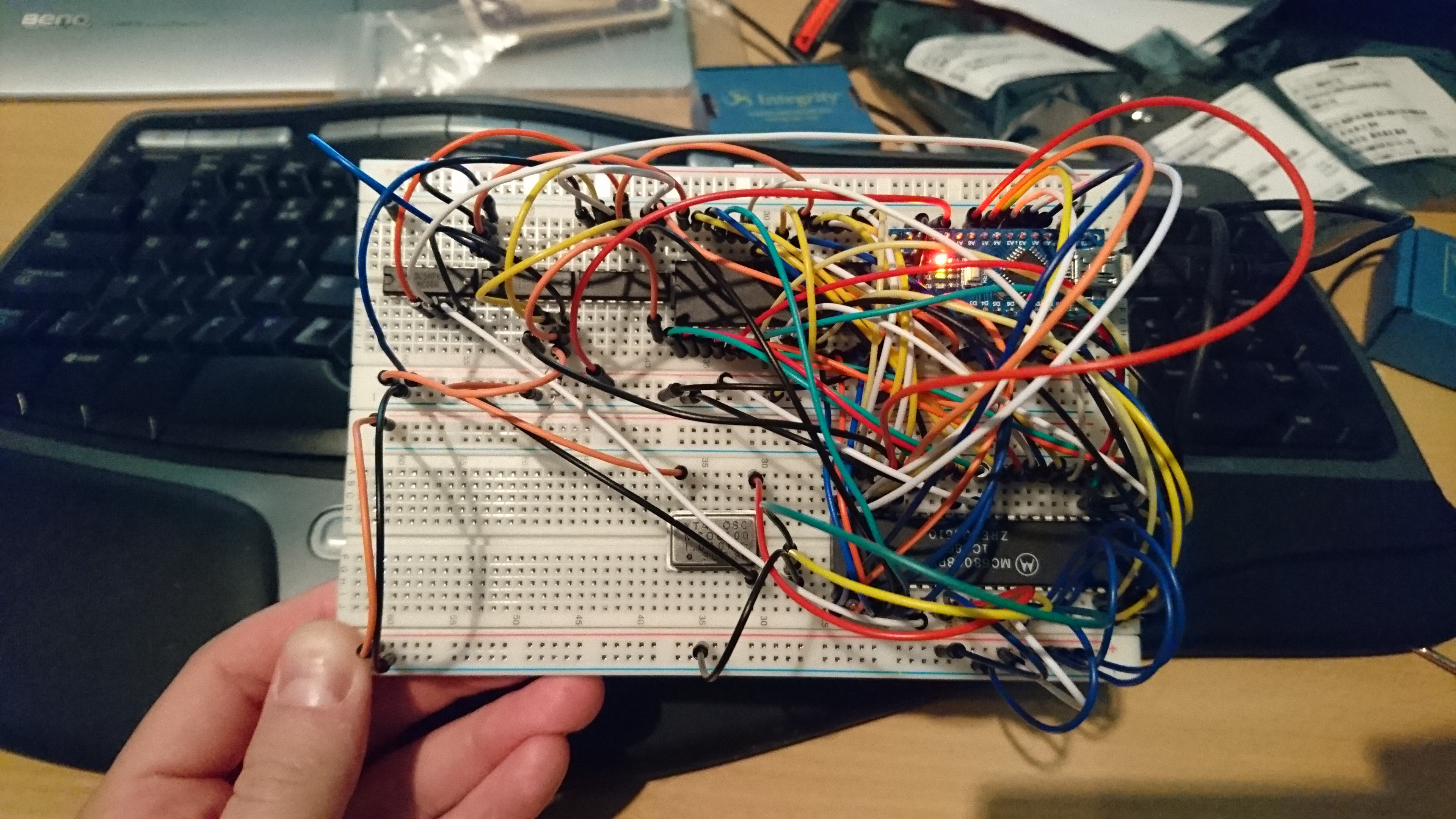

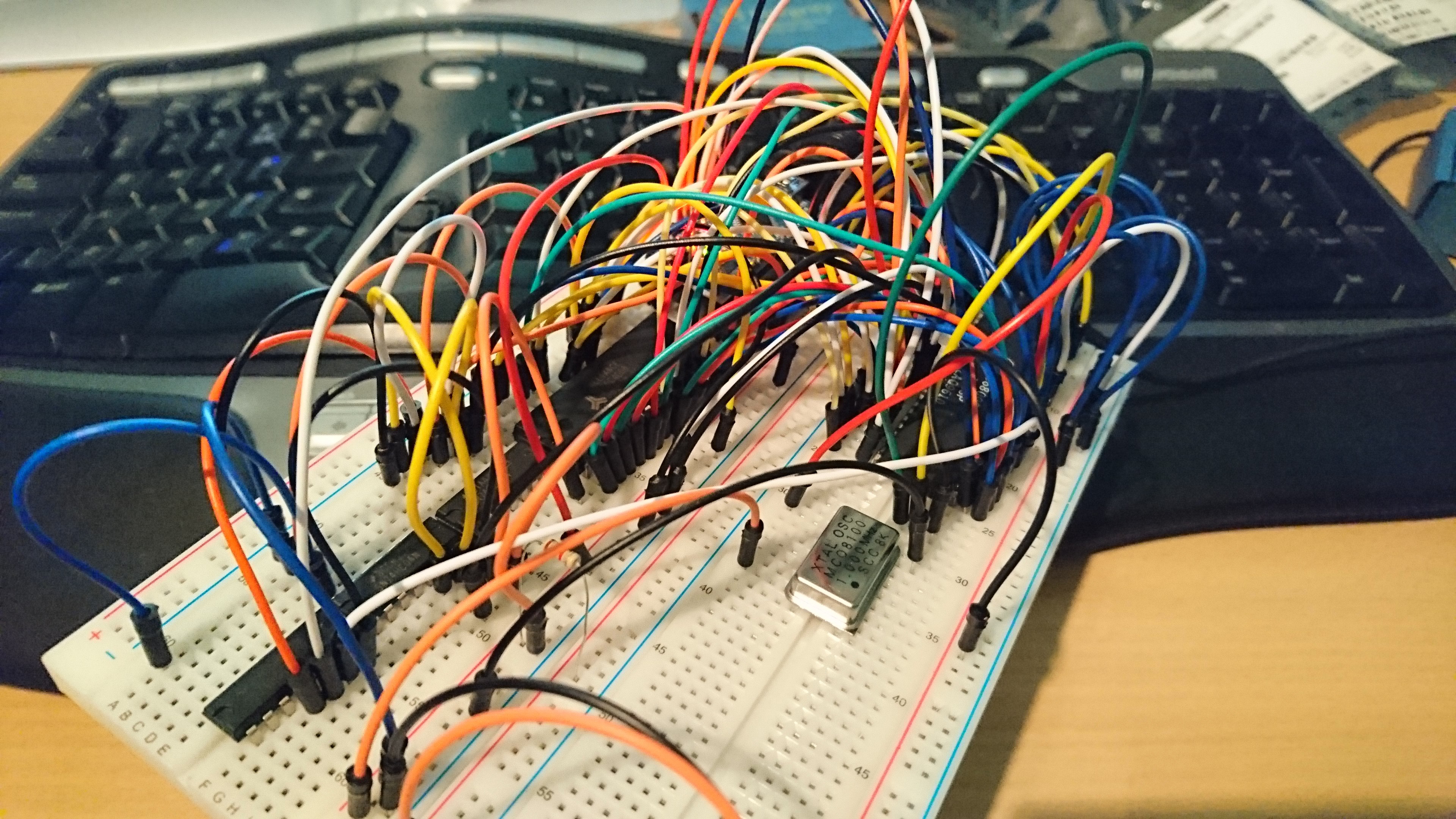

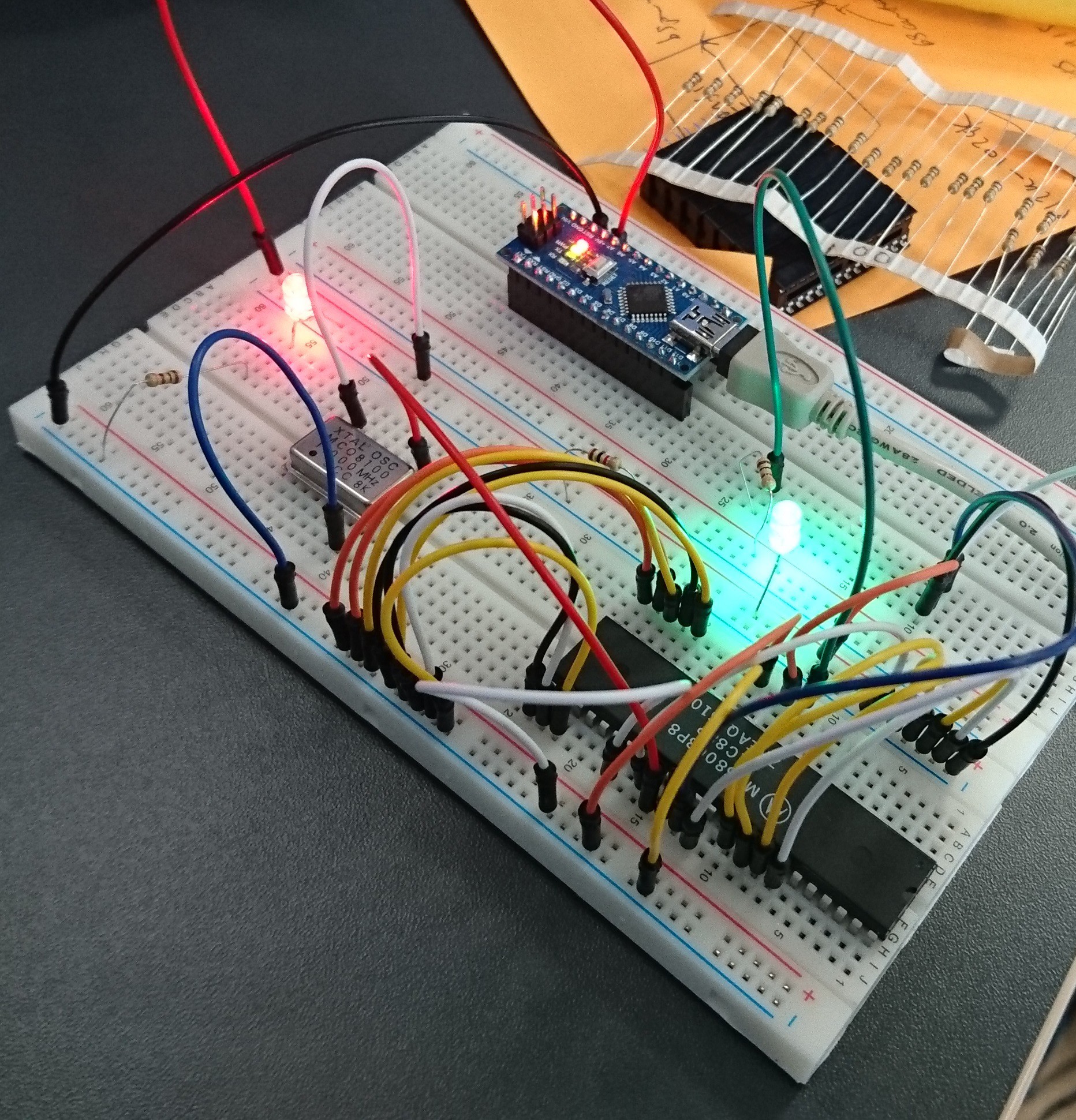

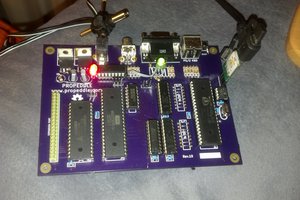

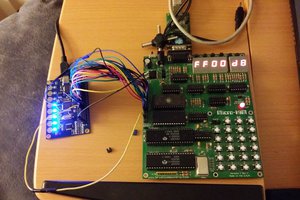

So after randomly seeing a project somewhere showing a Motorola 68000 on a breadboard in "free running" code I was inspired to trying this simple circuit myself as a project for the winter.

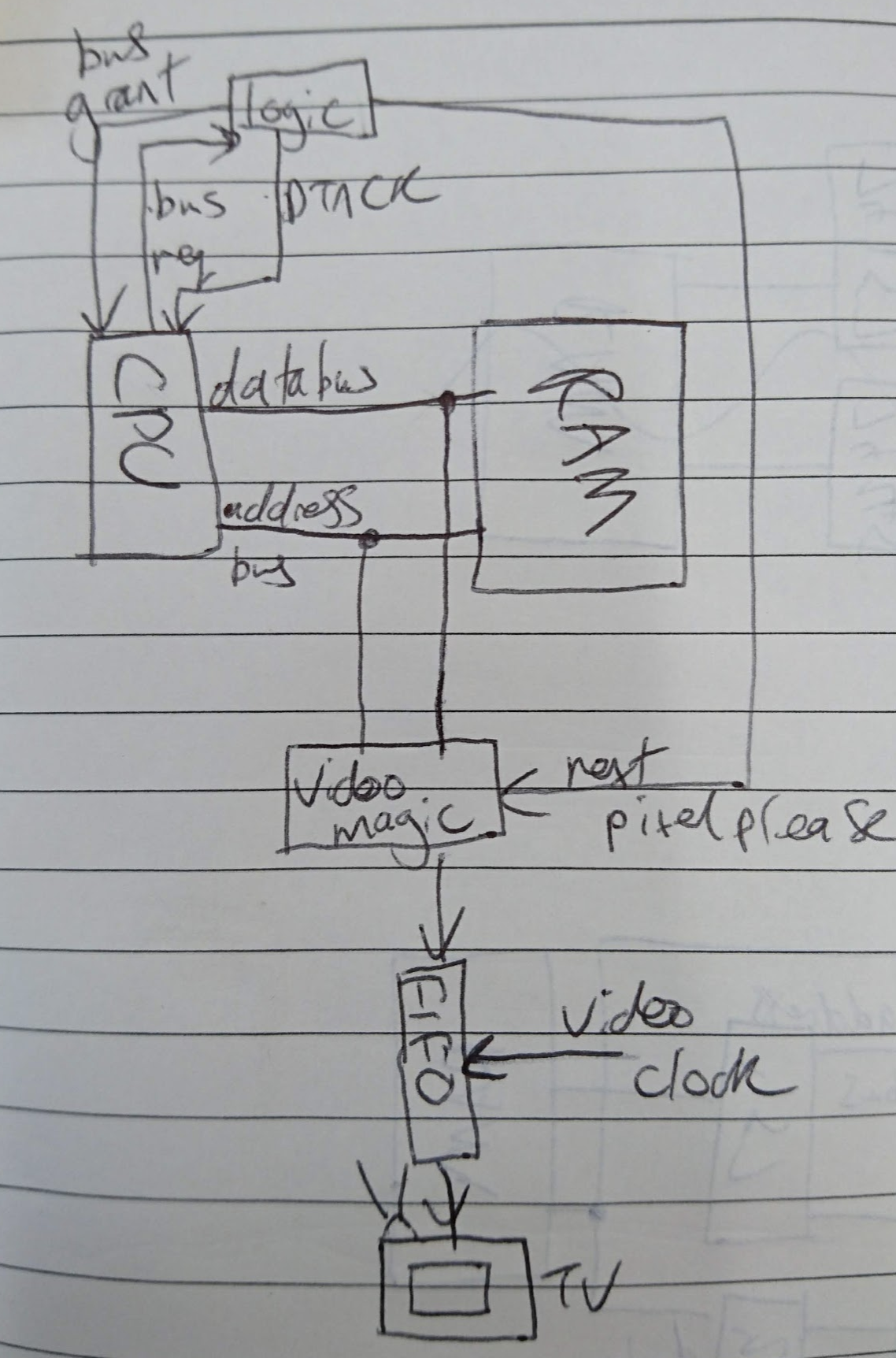

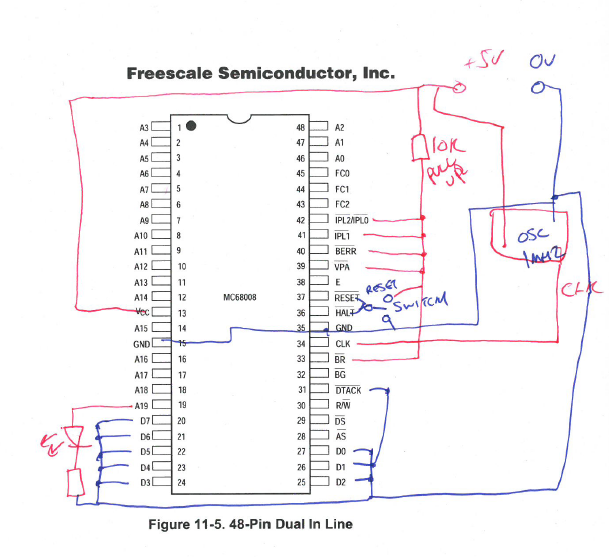

This project is me going from that original circuit all the way to a mini games console. The current aim is making a 4 MHz 68008 powerhouse with 512 KB of RAM, a TV out and two joystick ports. An Arduino provides all the I/O.

(much of this build log is me writing a few months retrospectively...I started this in October 2016)

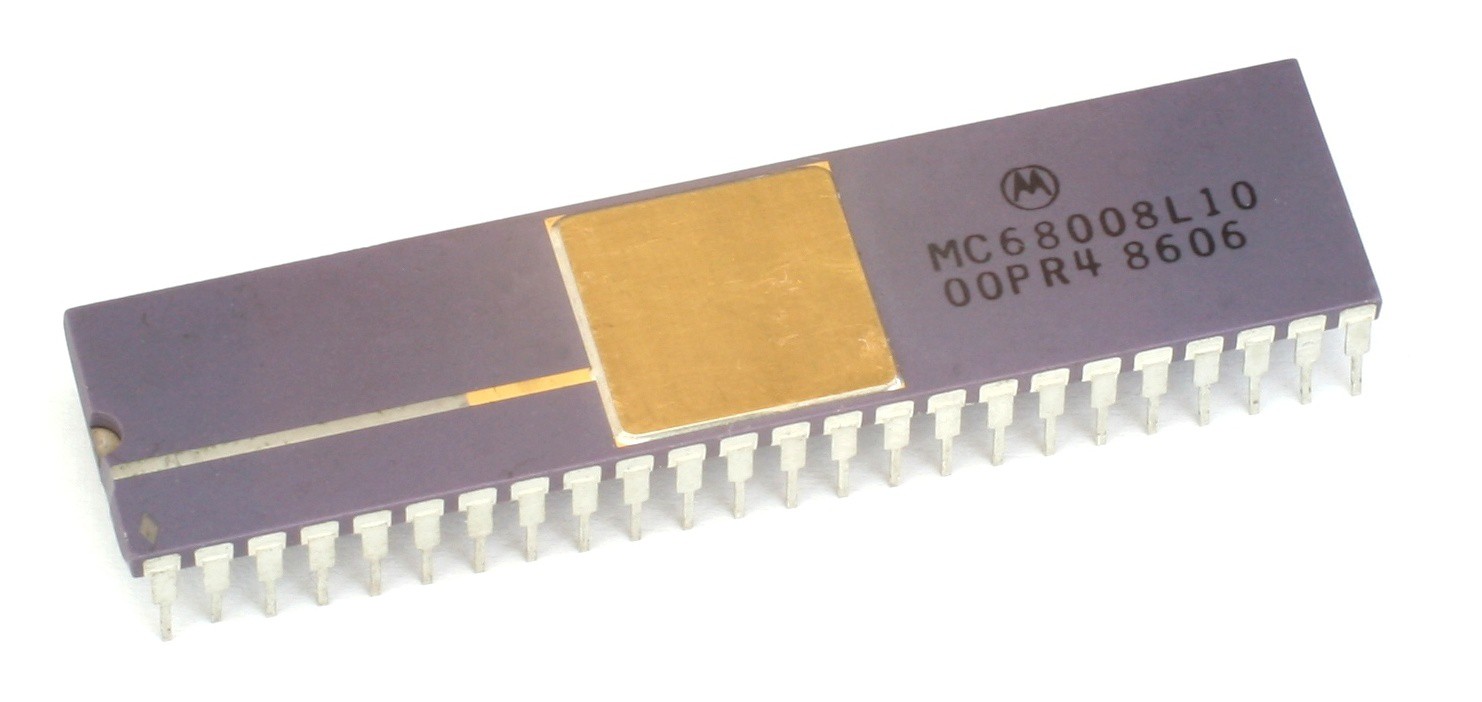

(By Konstantin Lanzet (with permission) - CPU collection Konstantin Lanzet, CC BY-SA 3.0,

(By Konstantin Lanzet (with permission) - CPU collection Konstantin Lanzet, CC BY-SA 3.0,  Notable connections

Notable connections

Jac Goudsmit

Jac Goudsmit

David Robinson

David Robinson

Ha yes I did indeed have 34 MB. The 2 MB chip which came on the motherboard and 'fast' 32 MB on the 030 accelerator card. People on classic Amigas nowadays often have 128 MB!

You are right though. Filling the memory can take a couple of seconds.