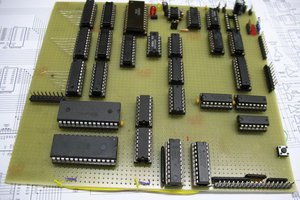

Have a look at the #Discrete YASEP project :-)

I think it got overwhelmed by its inherent complexity but it broke a lot of ground, for example with the #DYPLED display technology.

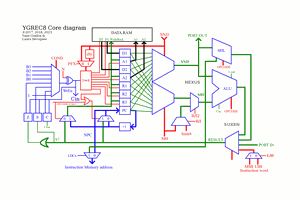

Then I started #AMBAP: A Modest Bitslice Architecture Proposal then #YGREC16 - YG's 16bits Relay Electric Computer then #YGREC-ECL etc. : the new architecture is somewhat simpler and leaner. However the register set's structure is a bit different and not adapted to the concept and organisation of #Discrete YASEP

Then I found out about the 74HC259 (see Enabling discovery) : this circuit (addressable 8-bits latch) is perfect for the bitslice register set. The rest of the circuit becomes a classic design now...

Logs:

1. First circuits and register set map

2. The ALU

3. Data Memory circuit

4. Parts, parts, parts...

Yann Guidon / YGDES

Yann Guidon / YGDES

jaromir.sukuba

jaromir.sukuba

Hah! Was going to say something like "CMOS?! I never thought I'd see the day..." But I see you're using 74HC chips, so, yahknow... TTL part-numbers, anyhow ;)