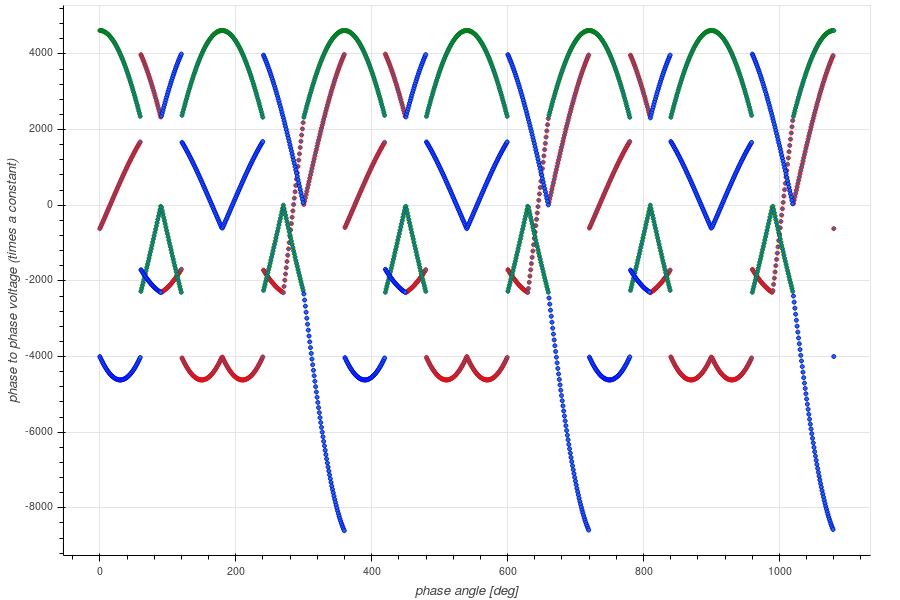

I'm implementing logic that takes as an input a voltage vector in space vector space, and outputs values that the pwm timers use to generate the inverter gate drive logic. I'm using Vivado-HLS to do this. I've written some code, C code! Eventually Vivado-HLS will turn that code into Verilog, but the first step is to create a test that runs on-laptop to verify that the C code to be transformed actually behaves the way it should before synthesizing Verilog from C. Here's the current output from the test:

When this is working as it should, it will look like three sinusoids spaced with 120 degree phase angle, not like three winking skeletons.

Adam Lange

Adam Lange

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

It looks more like dancing bunnies to me.

Looks like a couple offsets and a multiply and you'll be there. 3 bugs, maybe 4.

Are you sure? yes | no