Here's a peak at something I've been playing around with:

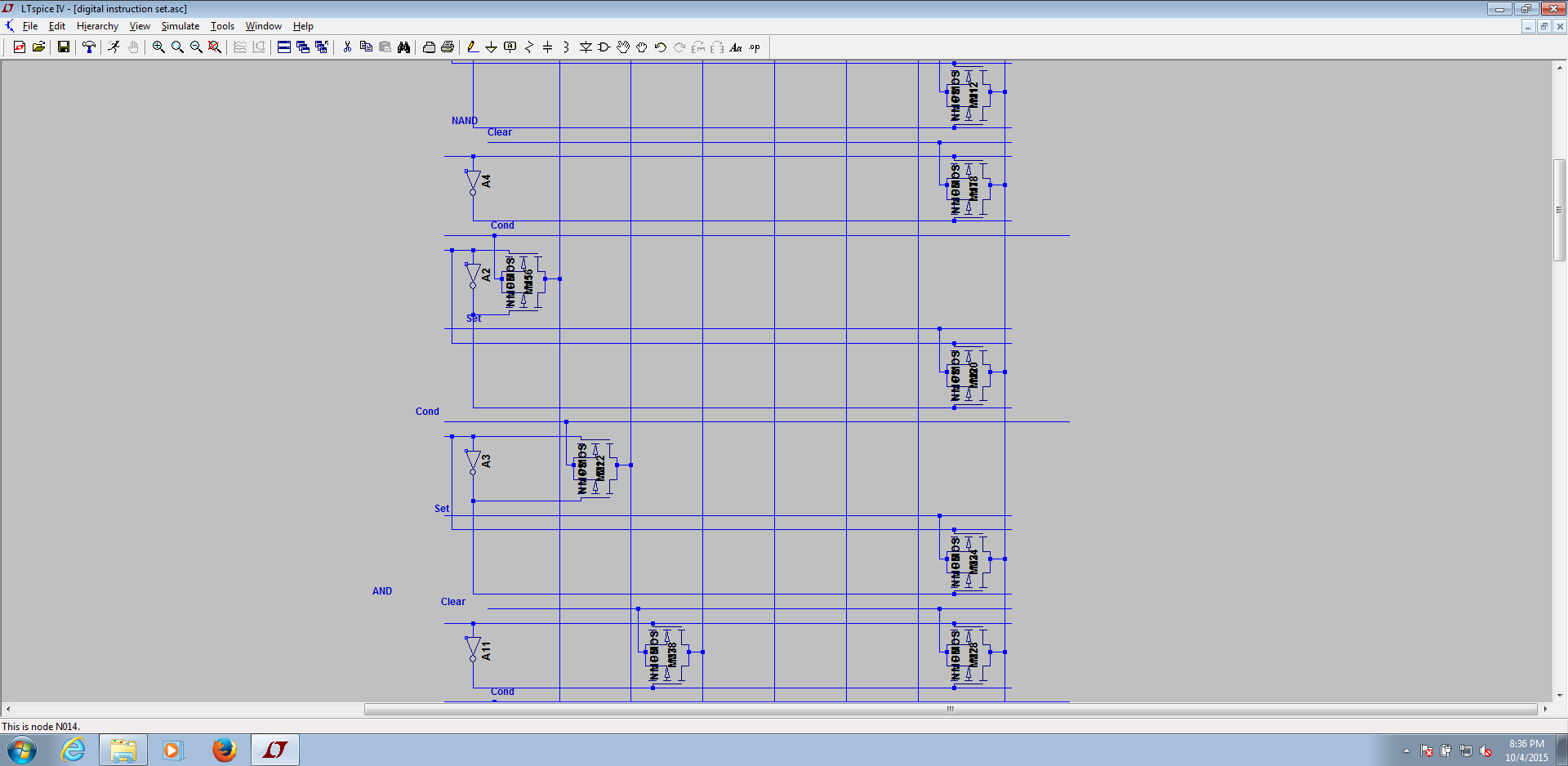

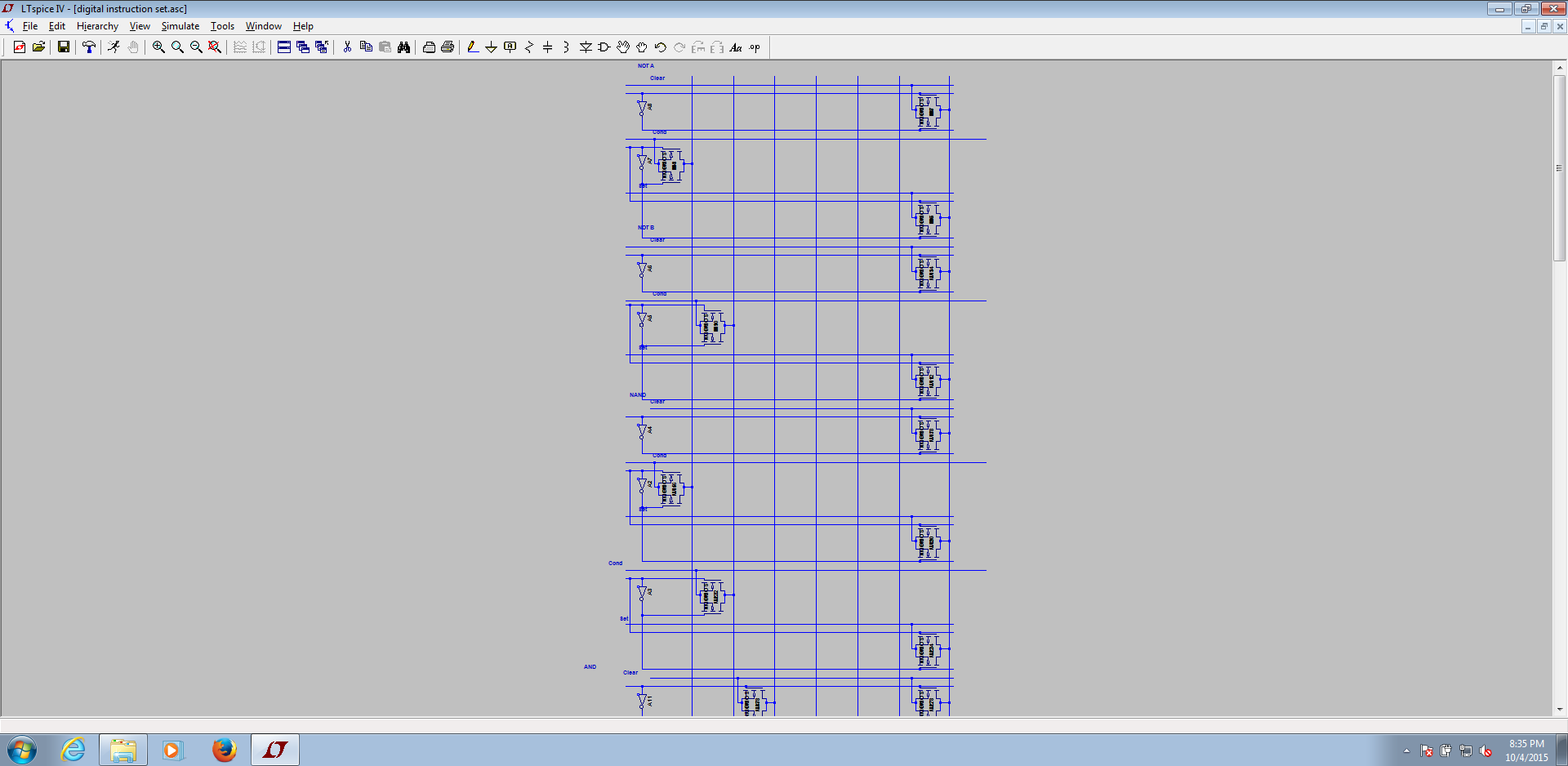

This circuit can be used to perform imply based logic functions. I've been implementing the previously posted digital instruction set. If anyone wants the exact spice file I'm using, message me. Each pair of transmission gates sends the corresponding Condition and Set signals required to perform imply operations. By moving downward sequentially, the correctly timed signals manipuate the memristor crossbar array connected to the vertical wires. This operation can be compared to the rotating barrel in a music box striking the correct notes at the correct time when directional force is appled. Different logic functions are grouped into sections.

This circuit can be used to perform imply based logic functions. I've been implementing the previously posted digital instruction set. If anyone wants the exact spice file I'm using, message me. Each pair of transmission gates sends the corresponding Condition and Set signals required to perform imply operations. By moving downward sequentially, the correctly timed signals manipuate the memristor crossbar array connected to the vertical wires. This operation can be compared to the rotating barrel in a music box striking the correct notes at the correct time when directional force is appled. Different logic functions are grouped into sections.

There are two ways I'm thinking of to trigger each row. One way would be to have a clock increment a binary decoder for the corresponding instruction, moving execution line to execution line with each clock cycle. Another method would be to have a decoder trigger the first execution line in an instruction, then have a delay buffer inbetween each execution line move through the steps automatically until the last step is completed. The first execution signal and the last, delayed execution signal could be used to switch a basic latch to indicate whether the memristor controller is busy or ready. This would facilitate asynchronous operation in a system.

My starting point for the design of this controller was diode based ROM. Each addressed row of diodes provides the correct data output. If someone were to intergrate an EEPROM into a full grid of transmission gates, different logic functions could be microcoded. This opens up interesting possibilites for programmable logic.

Being that this memristor controller can store and process data, a basic CPU of sorts could be made with an X by X sized grid of these controllers. This grid of memristor controller units would have a 1:1 ratio of processing power to storage, FPGA technology could be used to route signals from one controller to another. Additionally, if each controller shares their vertical wires with a common bus, mass instruction propagation may be performed. This can be used to perform content addressable memory operations (compare word-length blocks of controllers with search key using an equality function).

I have come up with a timing set for ternary operations, but I'm not going to manually enter it into a grid in a blogposting. At the moment, it resides in an excel file. Message me if you're interested in seeing this. If anyone has any suggestions for secure and free filesharing solutions please let me know.

While I have put a lot of effort into material implication based memristor designs, there are other, possibly more efficient methods of processing with memristors. I plan on investigating as many of these methods as I can. This paper in particular covers many different memristor processing methods.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.