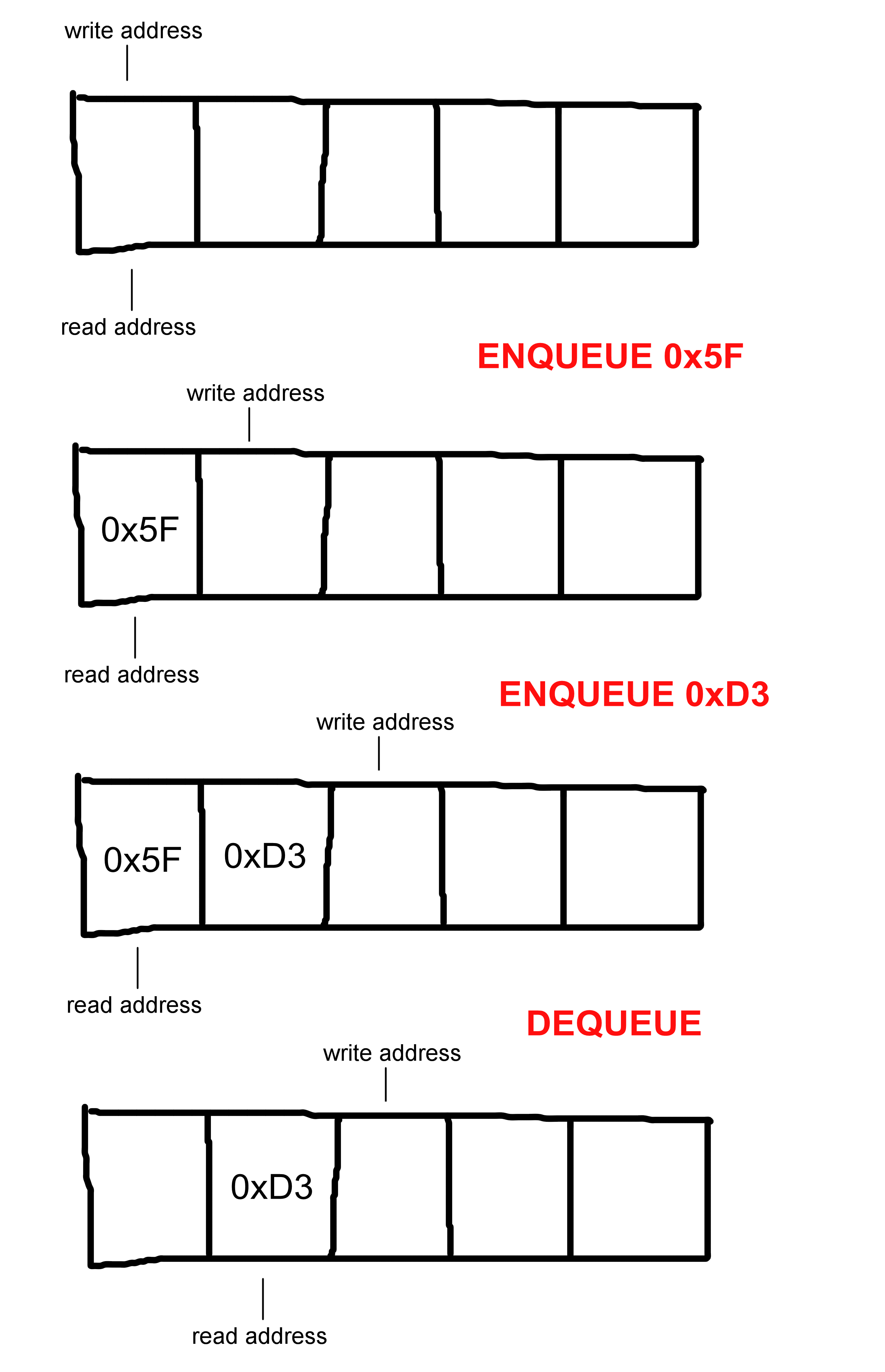

Slowly, but surely, the VHDL code for the controller is coming along; I've just finished a structural architecture for a FIFO queue (first in first out). In a FIFO, data is "enqueued" (pushed in a stack) and "dequeued" (popped in a stack). However, the cool thing about queues (and stacks, for that matter) is that only a value must be supplied; the stack handles addressing. Below is a sample of enqueueing and dequeueing using a FIFO queue:

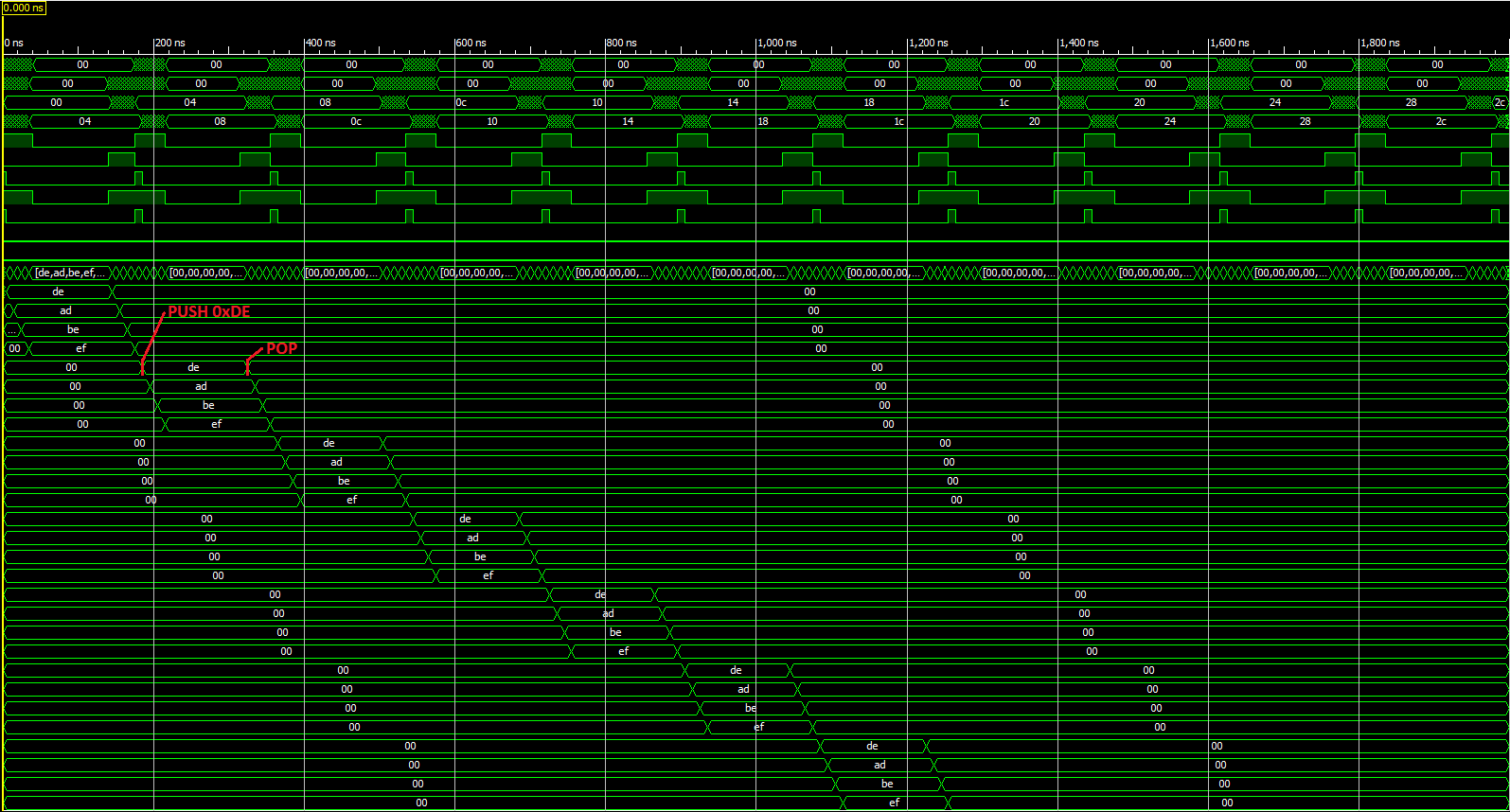

iSim Waveform of FIFO simulation (vhdl on github)

Reed Foster

Reed Foster

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

FIFOs are notoriously tricky designs. The synchronous version is easier though.

I'm trying to understand how you made yours, I should read the source code instead of decyphering the waveforms :-)

May I recommend GHDL for simulation ?

Are you sure? yes | no

Yeah, the waveform is more for show than actual documentation. Also the test code that I ran for the simulation doesn't fully demonstrate the stack because it reads all of the data out of the FIFO. I'm pretty happy with iSim for debugging because all I have to do is click on a button in Xilinx's IDE and it runs the simulation for me, but I'll be sure to check out GHDL though.

Are you sure? yes | no

I developed the 3R block with GHDL, which is very strict so I'm sure the code can be ported almost anywhere. I'm reading your source code now :-)

Are you sure? yes | no