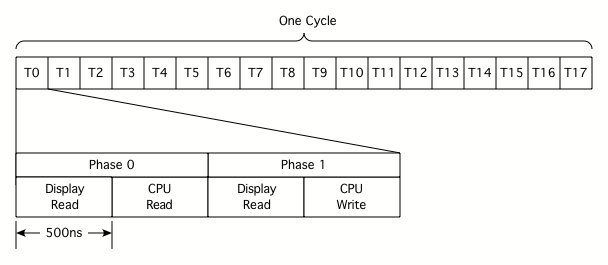

BREDSAC will operate on an 18-bit basic cycle, corresponding to a short word.

Because some operations require reading and writing back to the same

register, each bit time will be divided into two phases. In the first

phase a read may occur, and in the second phase a write may occur.

To allow for generation of the memory and register oscilloscope

displays, each of these phases will be further divided into two

subphases, one for the display system and one for the CPU.

The RAMs I'm using for the main memory and registers both have a cycle

time of 500ns, giving a bit time of 2us. Coincidentally, this is the

same as the bit time of the original EDSAC. However, the EDSAC had a

variable memory access time due to the need to wait for the word you

wanted to come around in the delay line, which could take as long as 32

short word times, or 1.152ms. The BREDSAC, with truly random access

memory, will be considerably faster.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.