PCB Routing

When I first looked at this a few years ago, all I could really find was the "Channel" router algorithm. It was "as plain as day" that the "normal" auto-router was based on shortest path (or some variant), but not much was published.

The Channel Router

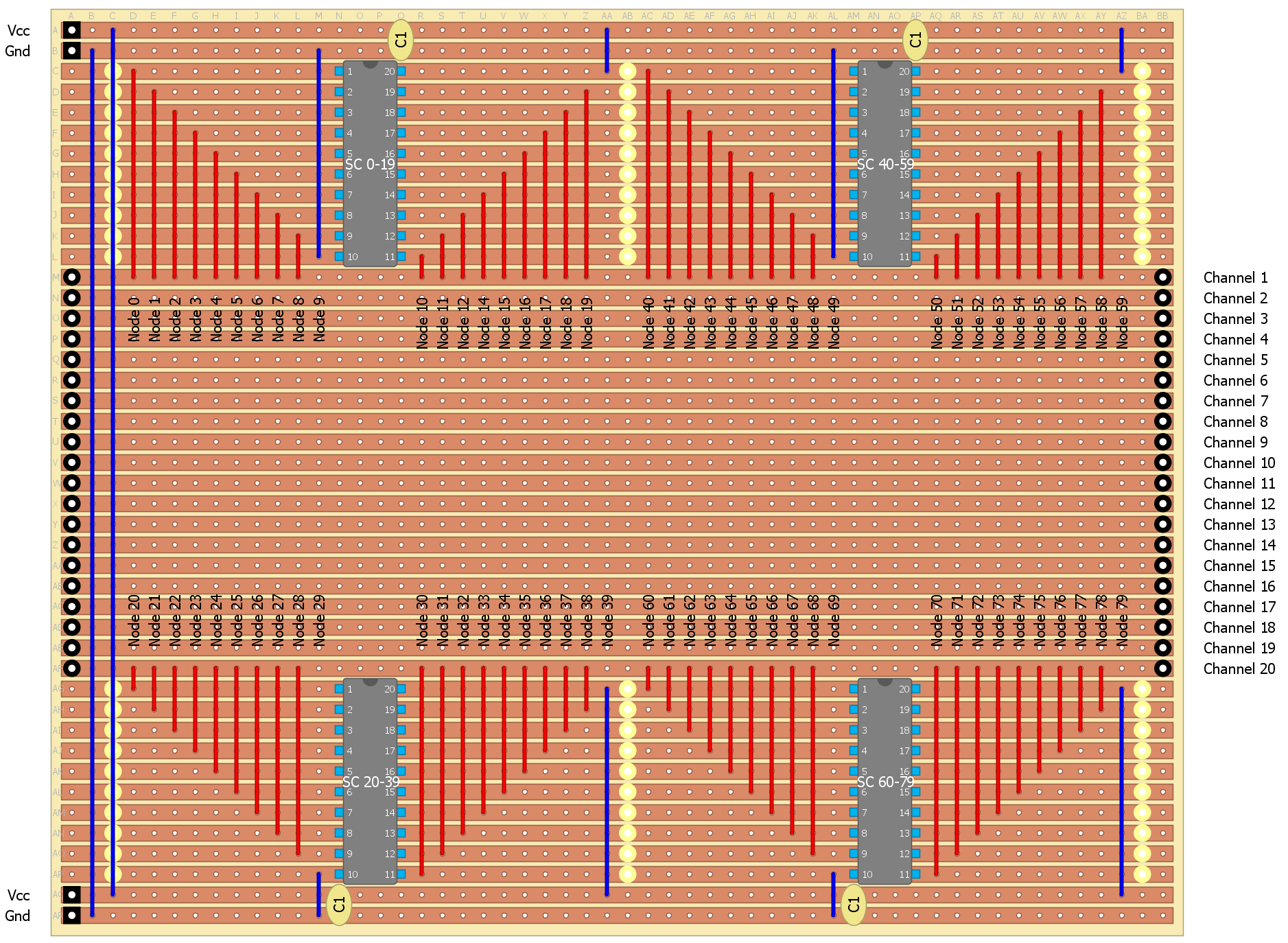

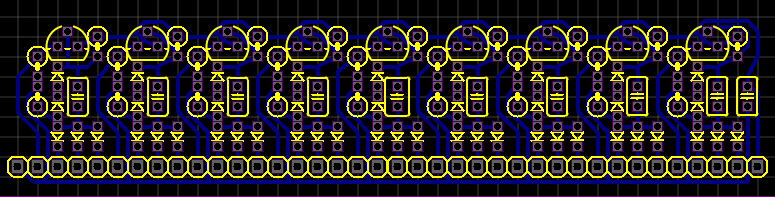

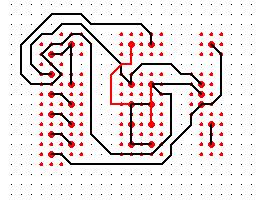

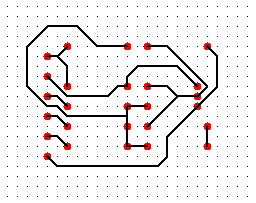

The Channel router is certainly an interesting problem. I looked at it for routing strip-board. Here is the concept, layout your components either side of a "channel" and the Channel router will link them up. Here is my proposed strip-board layout:

Note: the ICs can be replaced with individual components.

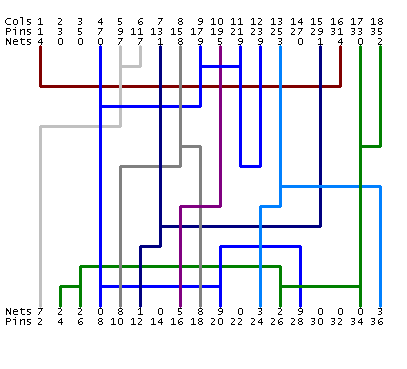

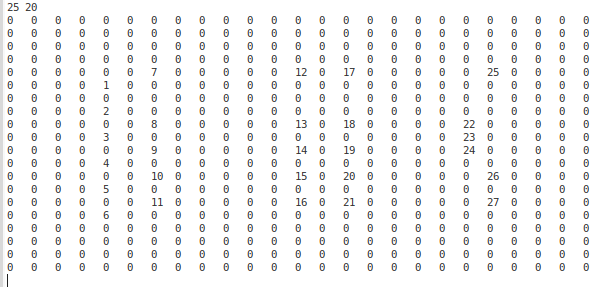

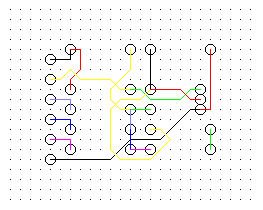

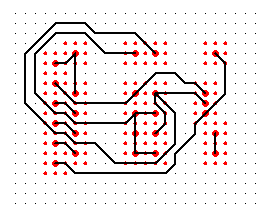

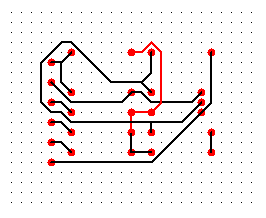

And here a typical "channel" wiring diagram:

Note: The Channel algorithm has been modified to suit the strip-board constraint of one wire join per location (or hole).

So it is possible to auto-route strip-board efficiently (from an algorithm point of view) but it is not that elegant (visually).

It might have a niche if the parts are also auto-placed. But at that point I did not feel as if this was going to be a "useful" project to continue.

Shortest Path

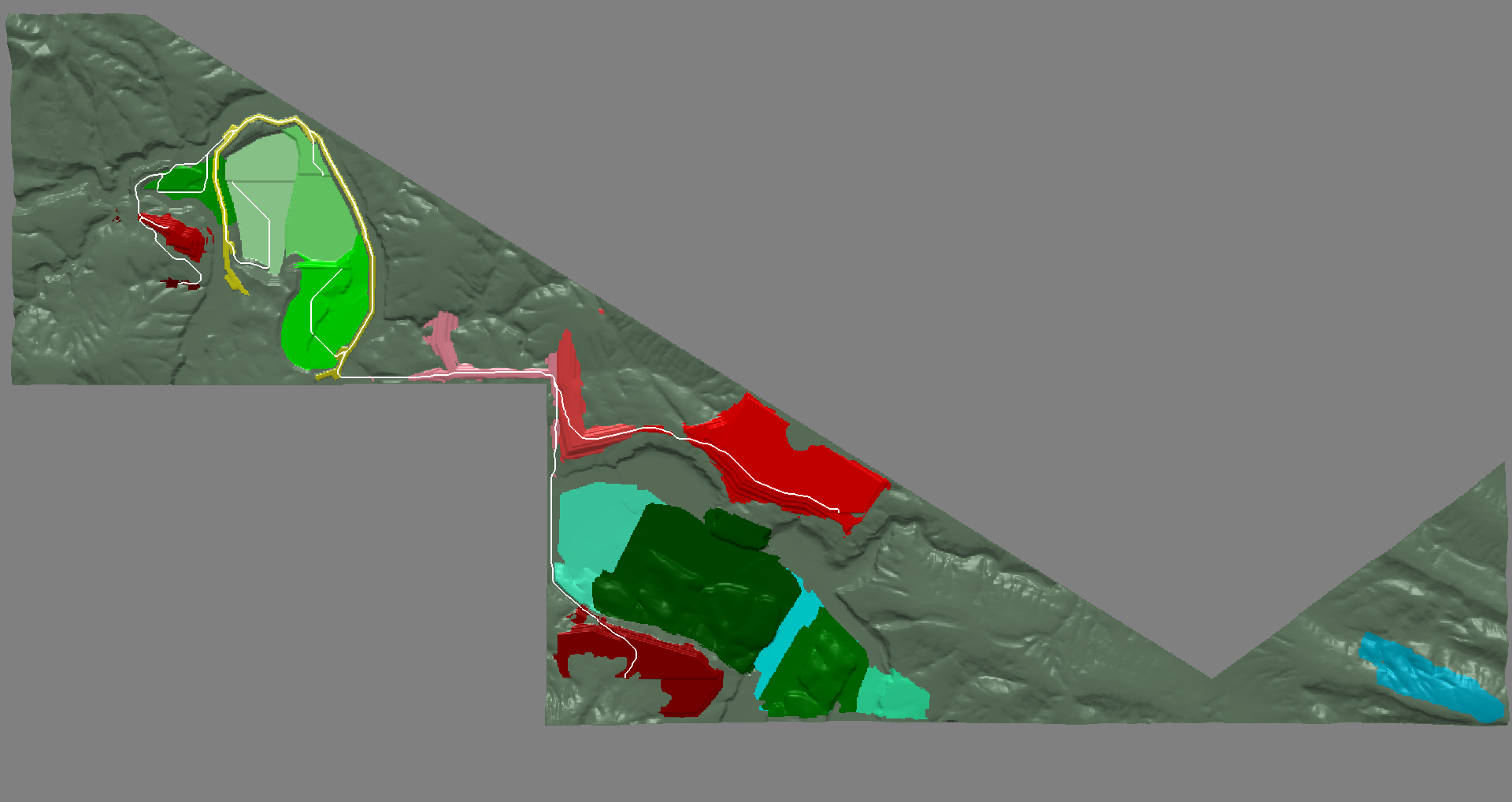

The shortest path algorithm is well known and I have used it n the past to determine truck haulage paths of open pit mines (yes I was a mining consultant in a past life). Here is an example (the white traces are the proposed truck haulage paths):

Note: the scale of this problem is quite large (i.e. about 10 km across).

So okay, I have used this algorithm before! So what is so hard about auto-routing?

AlanX

agp.cooper

agp.cooper

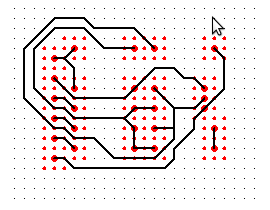

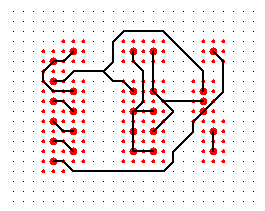

You can see that the congestion penalty has moved the tracks away from the pins (and other tracks) leaving space for later tracks. This in my mind is a pretty good result (for a single run). Without the congestion penalty you get:

You can see that the congestion penalty has moved the tracks away from the pins (and other tracks) leaving space for later tracks. This in my mind is a pretty good result (for a single run). Without the congestion penalty you get:

gertux

gertux

Pnoxi

Pnoxi

Kai

Kai

Hi Ken,

Added support for image rotation. So I have something useful now. Next would be to export the nets and the board outline.

Looking at my code, it is not great but it is functional. I read the S-Expr name and depth and what ever list item number I need. I join the fragments with associative arrays. Final I export the associative arrays for further processing. It is hard coded so I just need to know all the possible cases.

A LISP or Prolog programmer would probable only need a few 10s of lines of code to do the same job.

I have other things to do today, so I will have another look tomorrow.

---

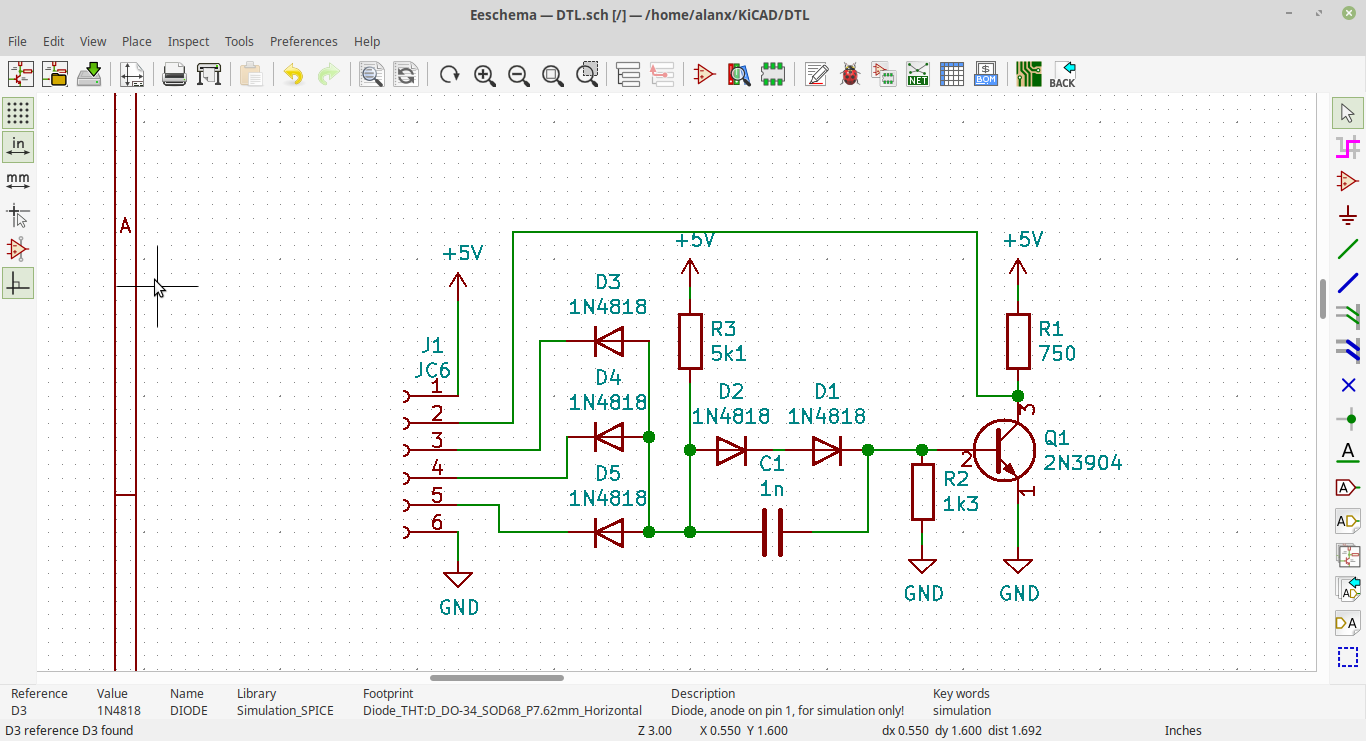

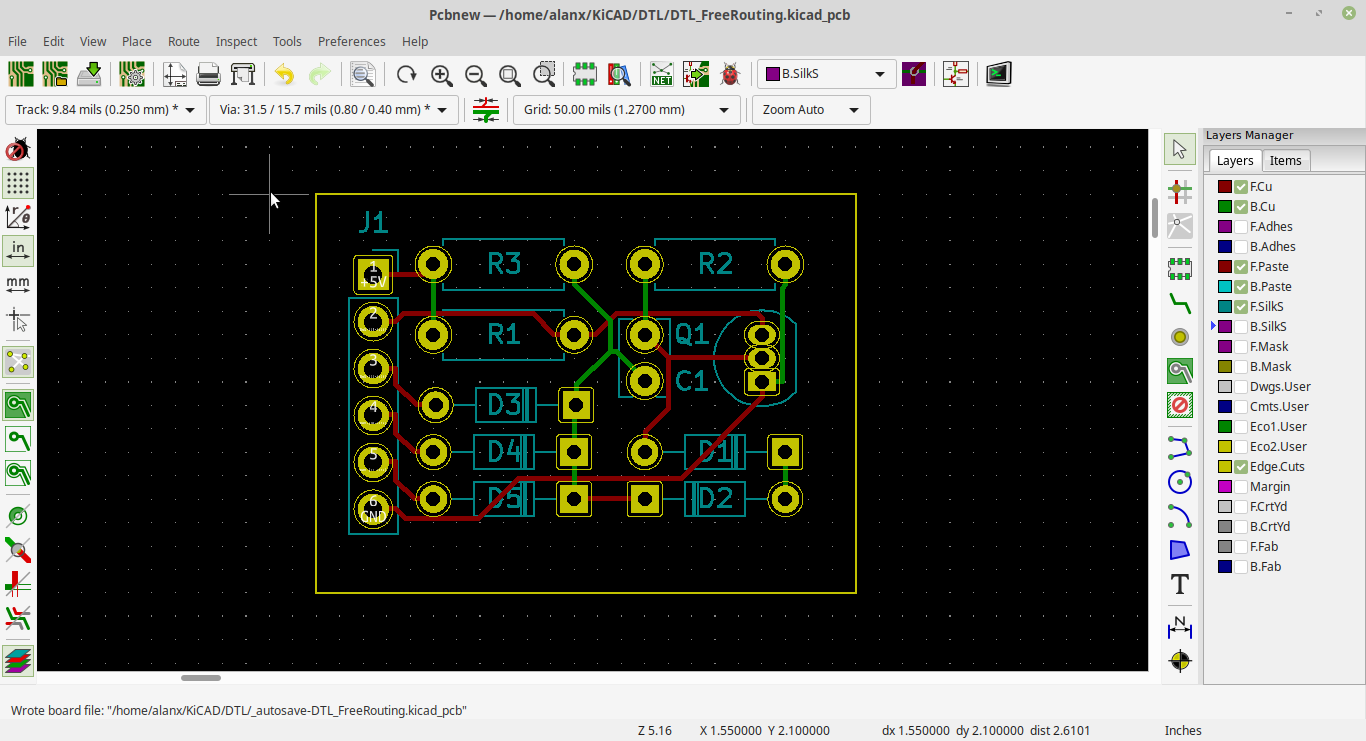

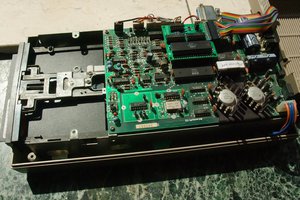

I have designed a new version of my CP/M machine. This time with external timers and a UART. I have upgraded the flash drives from 32k to 256k. The only problem is I have only been able to auto-route a 4 layer board.

AlanX