LM555 with serial output,

ok, I'll try to attack this in layers....

First, serial data transmitter.

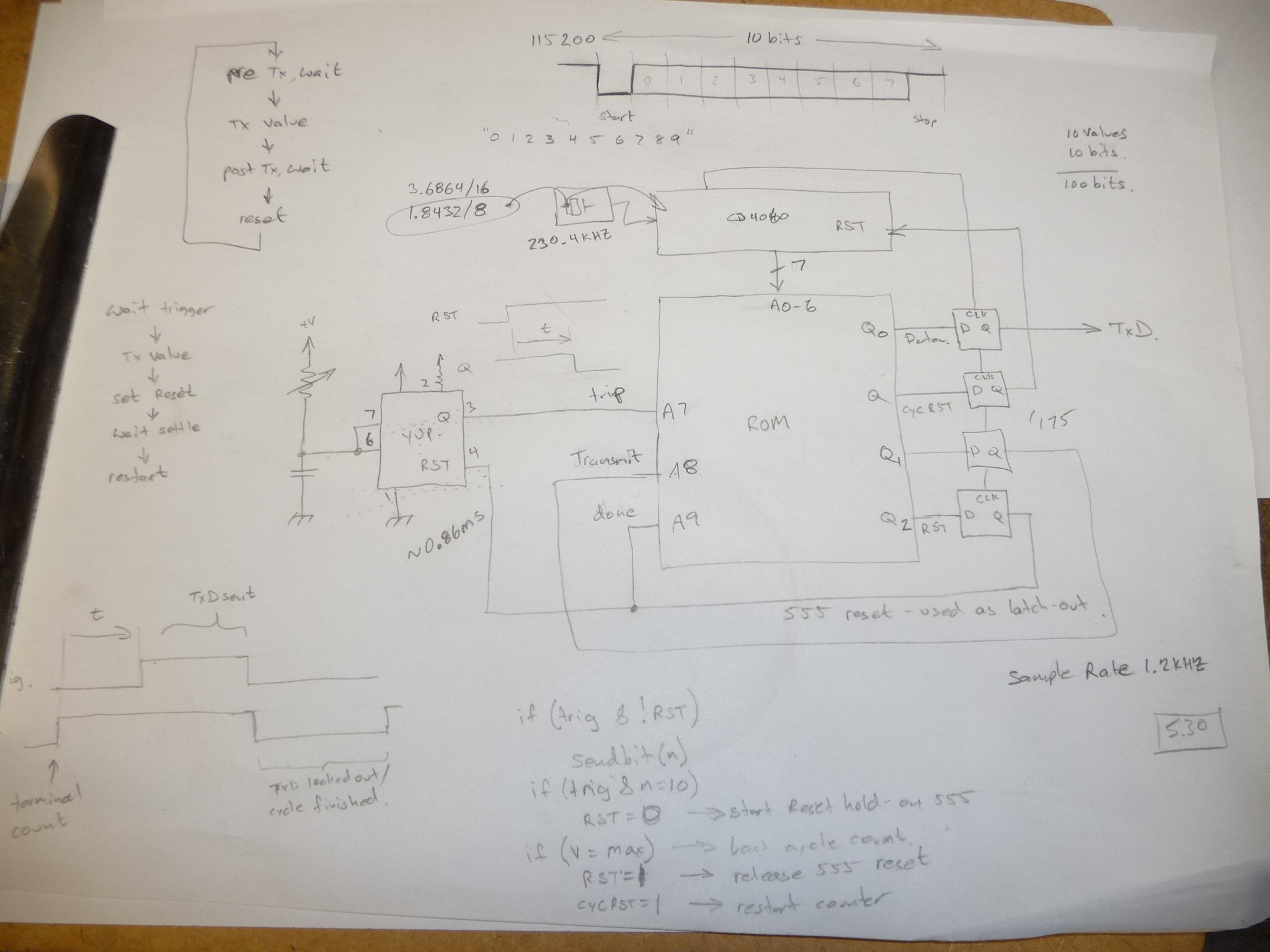

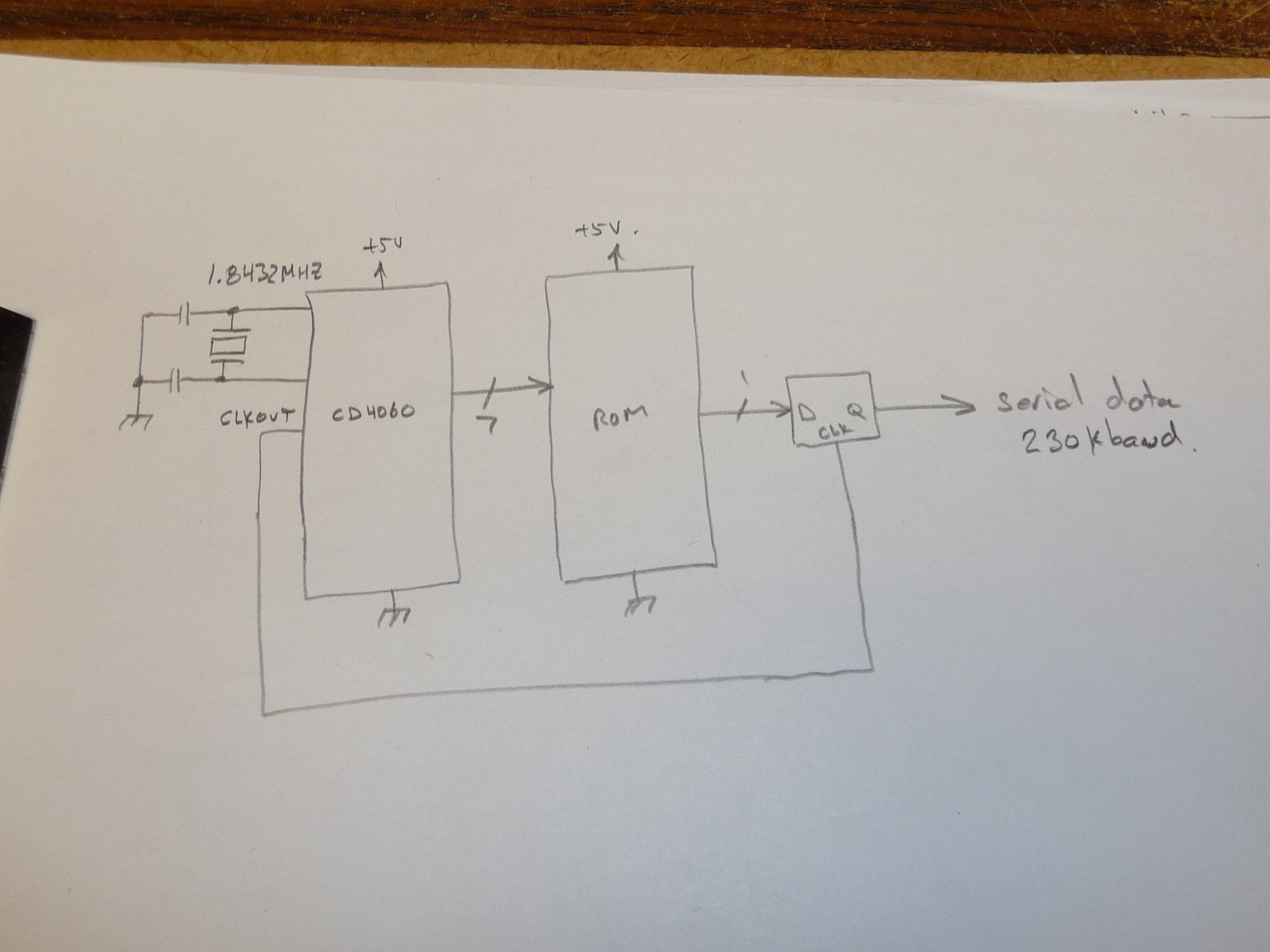

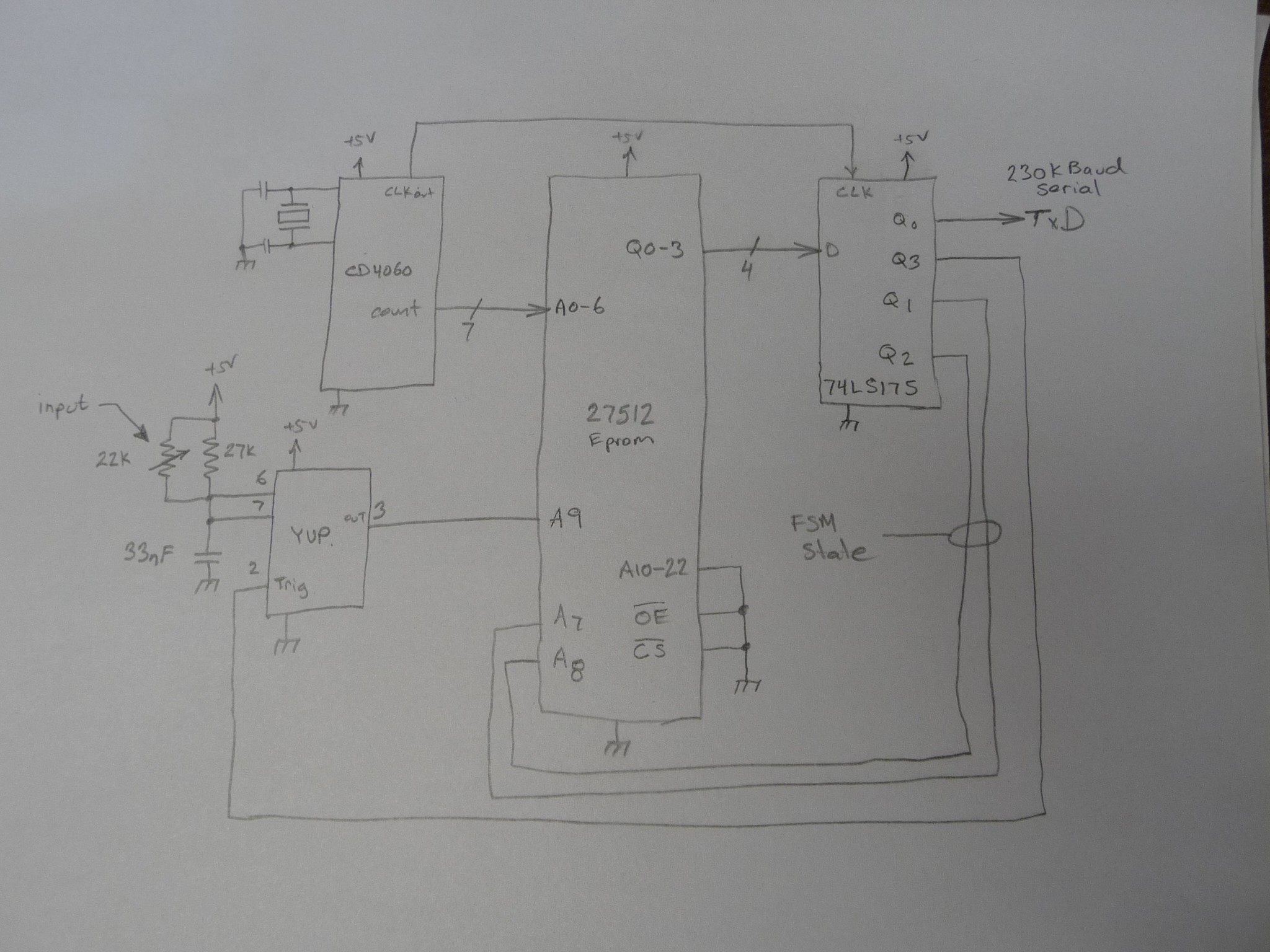

The idea is to have a serial bit stream stored in a ROM, addressed by a counter.

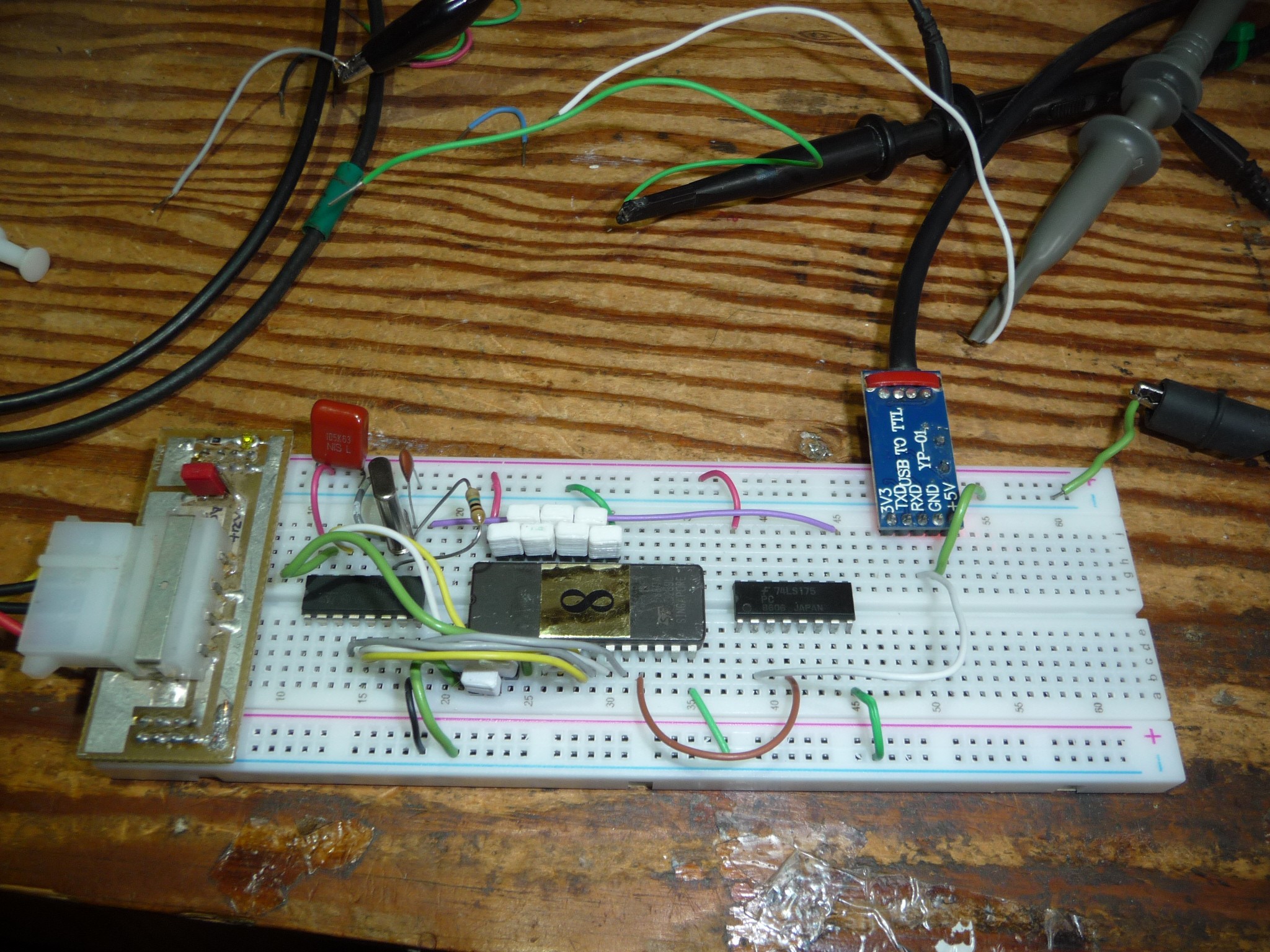

The 4060 is a counter that has built in oscillator hardware. Running it with a 1.8432MHz crystal provides a 230kbaud (2x 115200) we get a 7 bit count.

With a 7 bit counter there are 128 bits available for a serial stream.

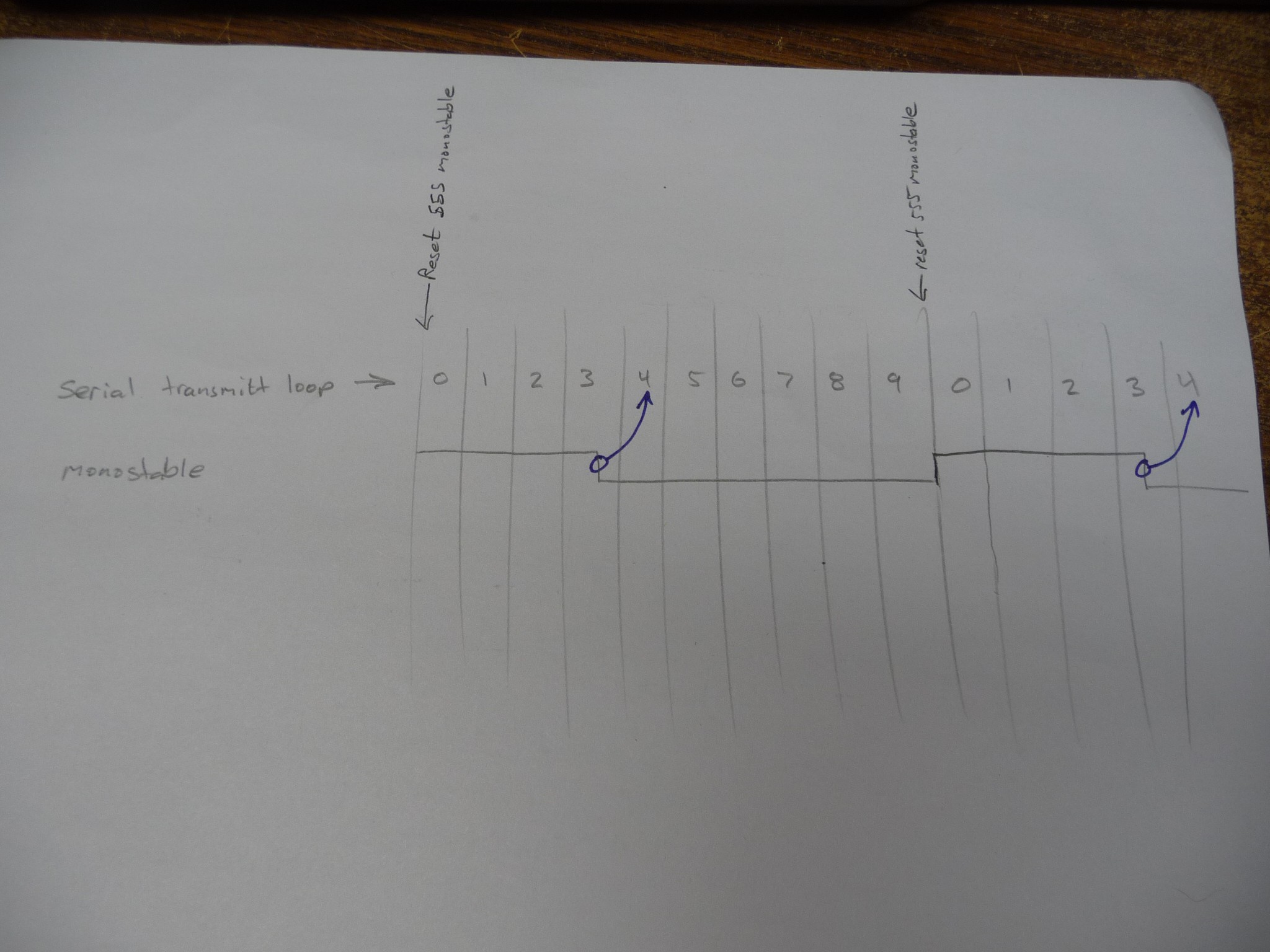

A serial byte takes up 10 bits (start, 8 data bits, and stop) [photo, top right]

So 12 characters can be saved in the stream. Thats enough, this only needs 10.

As the CD4060 is a ripple counter, the output will be messy timing wise, the ROM will not help. A latch can be used on the output to fix the timing.

A 74ls174 will do.

I'm feeding the serial to a TTL->USB adapter :)

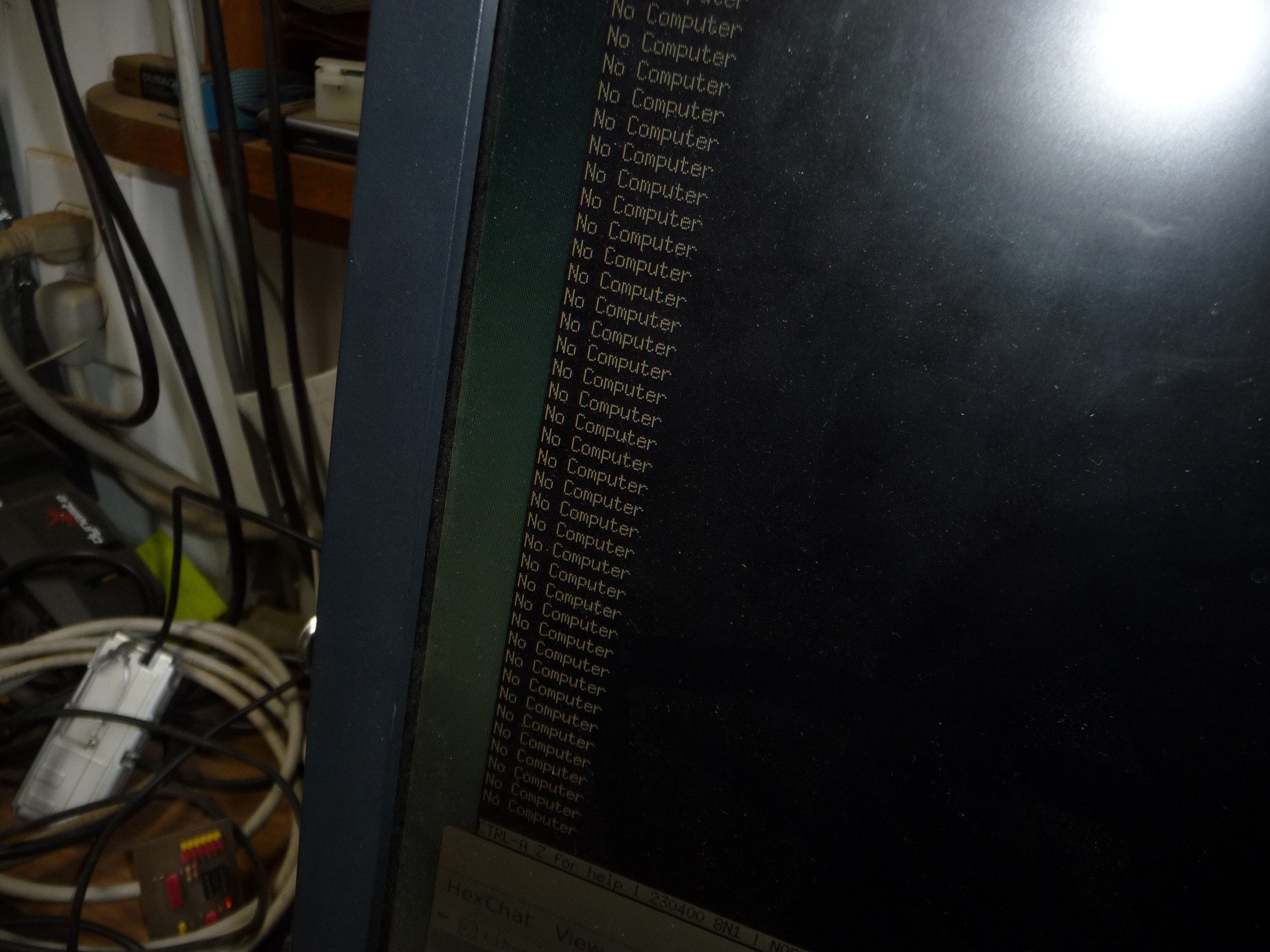

This will be able to transmit serial messages. be it short ones, like "No computer"

===============================================================

===============================================================

The ADC idea will involve running the 555 as a monostable that is synchronized with a serial bit stream from a ROM.

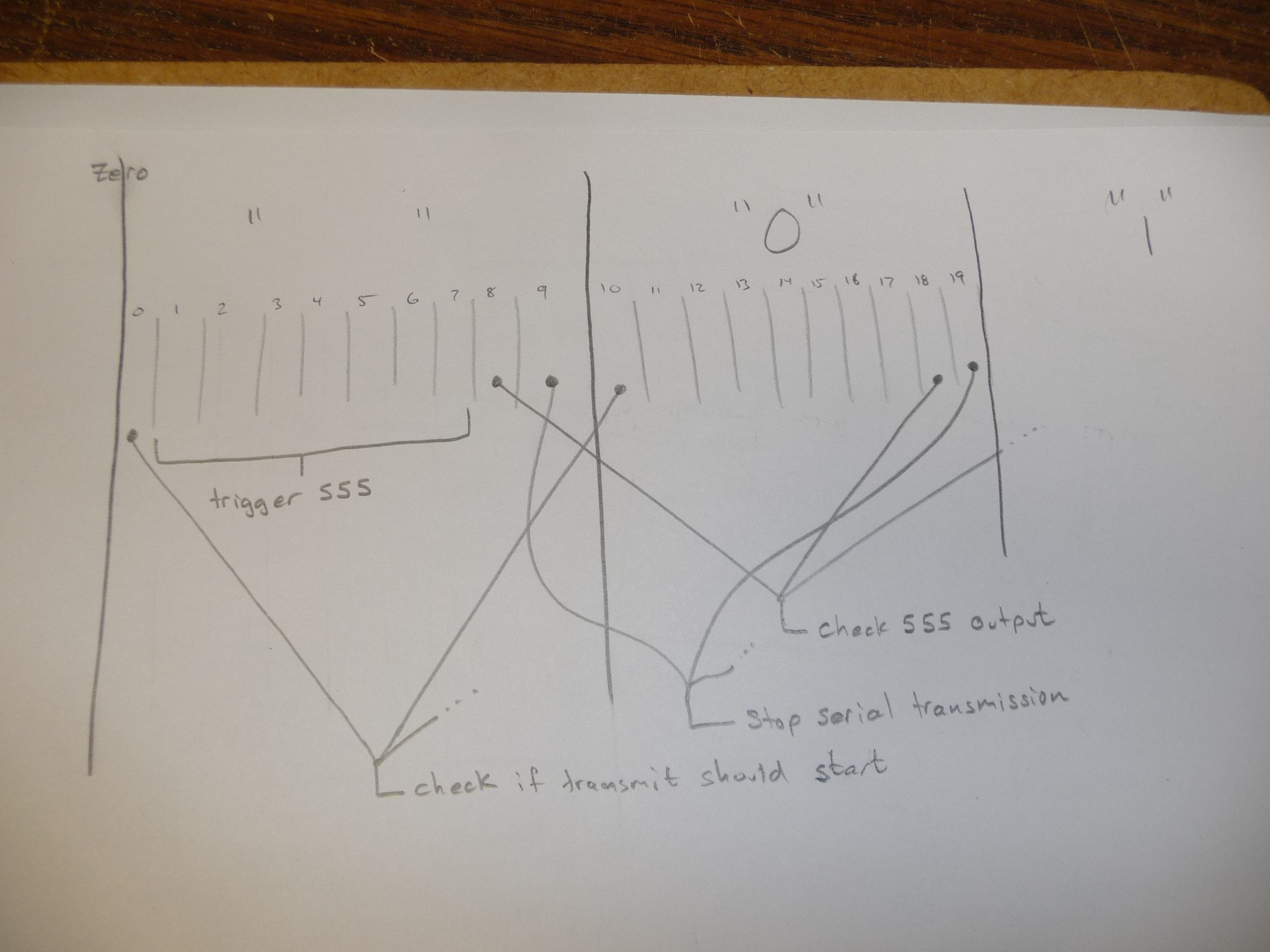

The bit stream will consist of the string "0123456789"

When the monostable times out, the next serial character is enabled to the transmitter.

In this example, the monostable trips during "3", meaning "4" is transmitted.

This gets complex for a few reasons.

This gets complex for a few reasons. You need to know if you should send the character by the first bit of its time space.

"0" starts immediatly, there is no time for anything to happen.

To allow time for zero, the string will actually be " 0123456789", the leading space gives time to reset the system and detect short pulses for outputting a zero value.

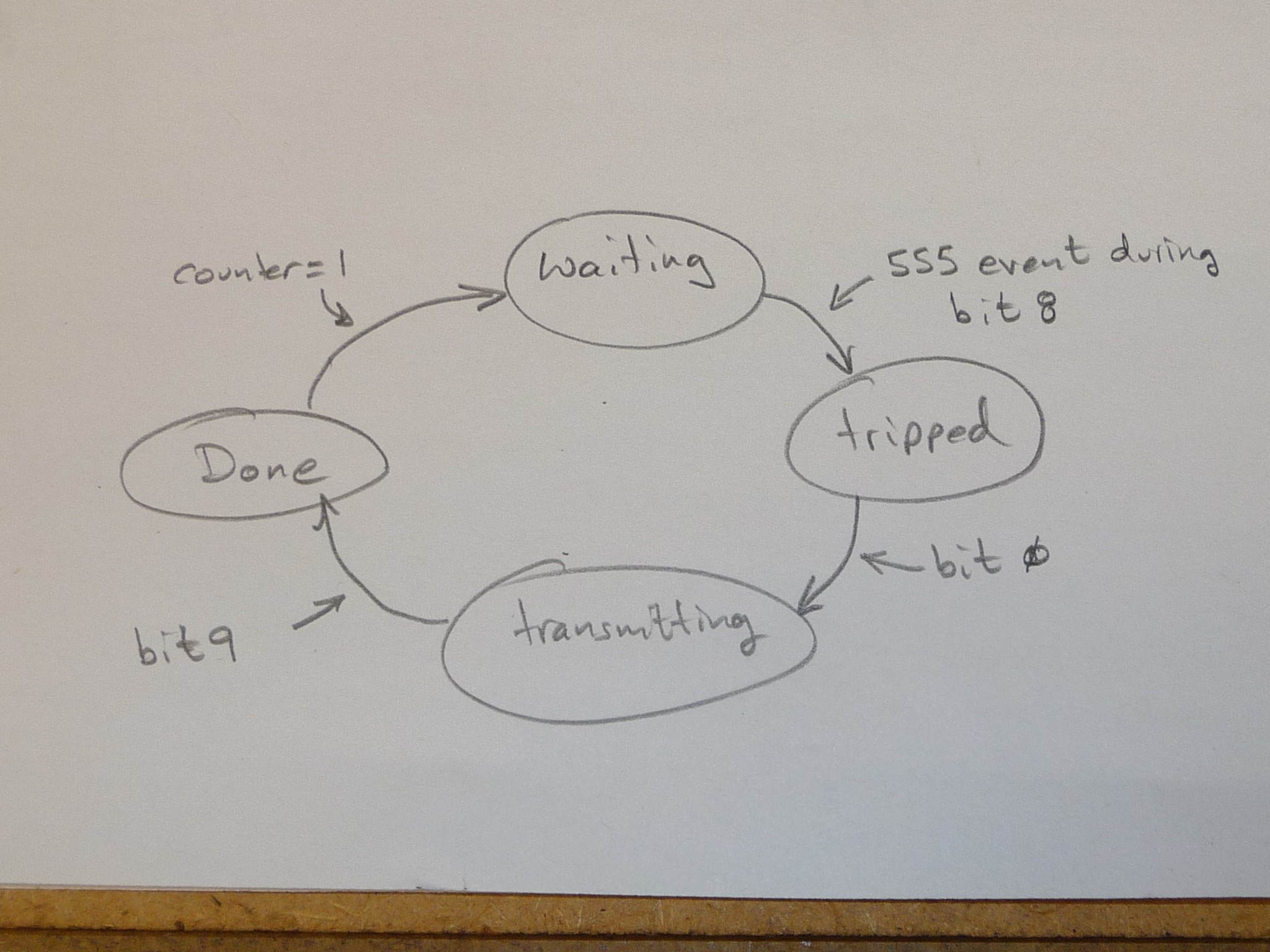

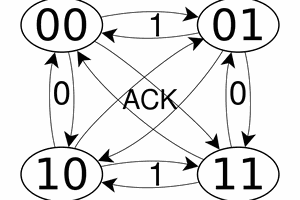

The system has no memory of the value when the pulse happened, To "gate" thru just one digit, we need a state machine that tracks whats going on, there are 4 system states.

- timing

- tripped

- transmitting

- done

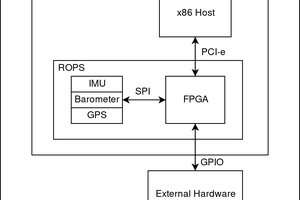

This requires 2 bits of feedback from the input to the output of the ROM, that loopback (thru a latch) creates what we need for a state machine.

The state machine starts in state 0 (waiting).

During counts 1-7 from the CD4060, the 555 is triggered, this ensures a long enough pulse to trigger it.

Every 9th bit-slot, the state machine checks the output of the 555, if its timed out, the state machine changes to state 1 (tripped).

Every first bit-slot the state machine checks if its been tripped, and if it has, changes to state 2 (transmitting)

Every 10th bit-slot, the state machine changes to state 3 if it was in state 2 (goes from transmitting to done)

===

===

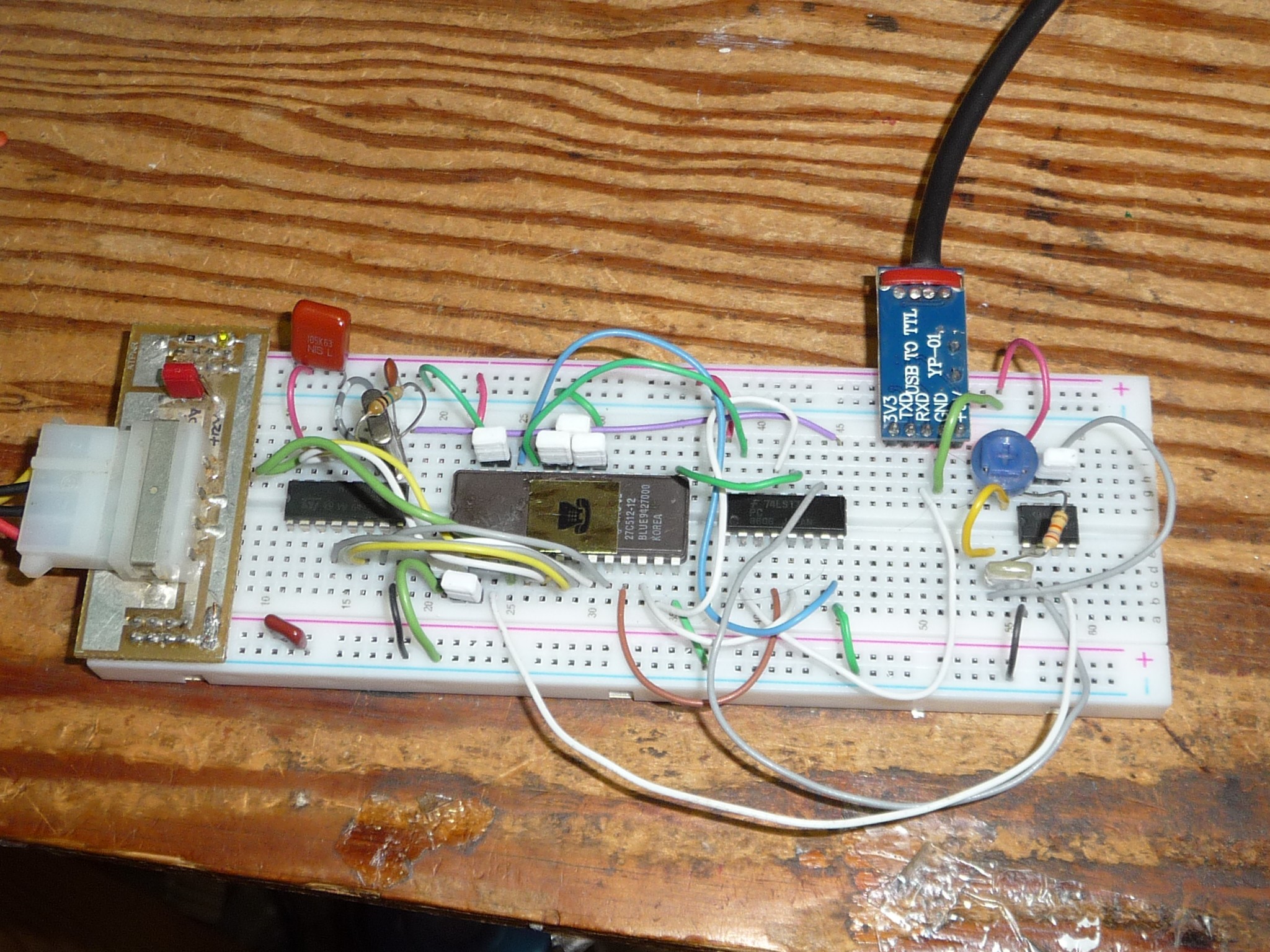

What the system look like so far:

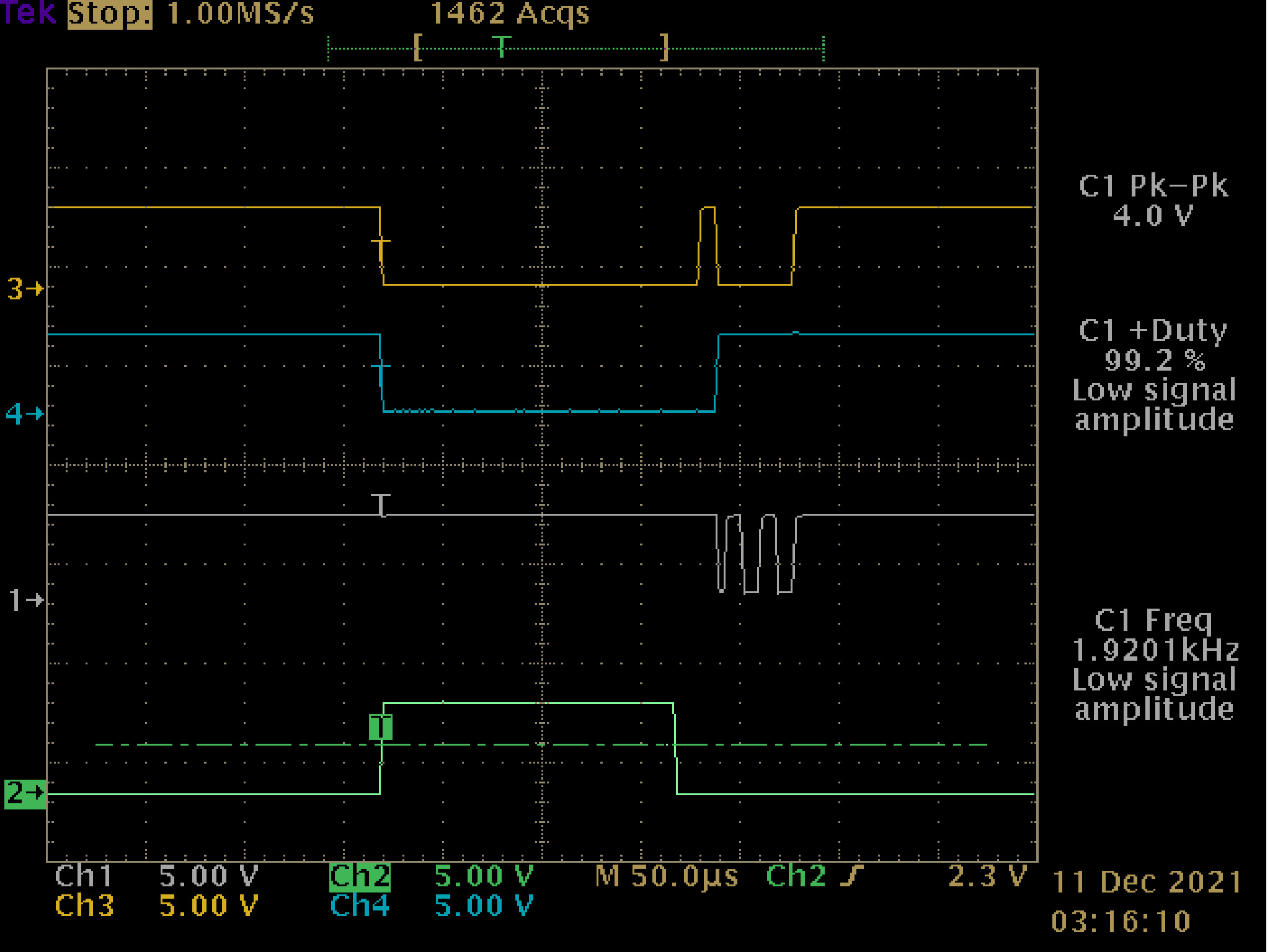

Timing waveforms:

The top two traces are the FSM state, at the start of a cycle they are set to 0

The top two traces are the FSM state, at the start of a cycle they are set to 0The bottom trace is the 555 output. When triggered, it goes high. After a time period defined by the value of the resistor, it drops back to zero.

The white trace is the serial data line.

On the 7th bit of the character transmit cycle, the 555 is checked, if its finished its cycle, the state machine goes from 0->1.

During the first bit of the chatacter transmit cycle, the state is changed to 2 if it is 1.

If the state is 2, the serial bits are enabled to the output.

On the 10th bit of the character transmit cycle, the state is changed to 3 if it was 2.

Rue Mohr

Rue Mohr

Al Williams

Al Williams

Yann Guidon / YGDES

Yann Guidon / YGDES

Haha, cool idea, using a ROM to generate a serial stream. 👍