An AND gate takes in two (or more) inputs, and outputs a logical 1 when all inputs are 1. All other gates can be expressed with AND gates, so if necessary other gates can be brute forced once this circuit is verified.

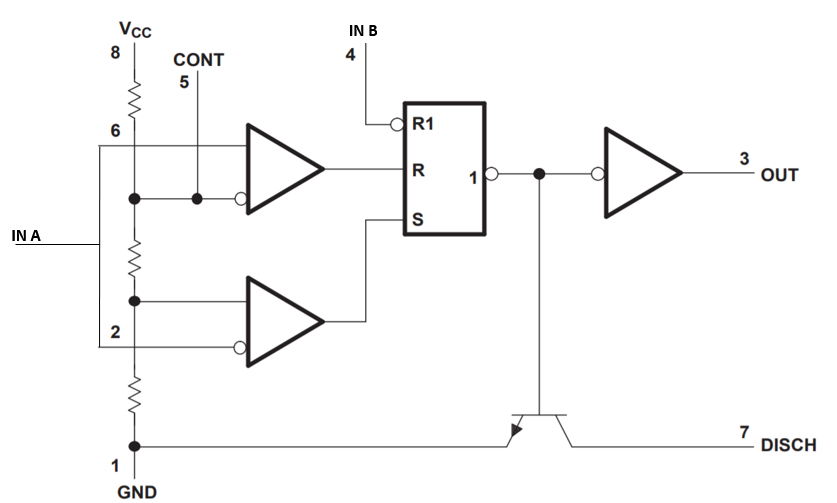

Consider the modified schematic shown in below. An AND gate with one inverting input can be constructed using RESET (IN B) and THRES/TRIG (IN A) as the gate inputs.

THRES/TRIG = 0, RESET = 0, OUT = 0:

Whenever RESET is 0, since the pin is inverting, the SR flip-flop output will be held at 0 in a reset or disabled state.

THRES/TRIG = 1, RESET =0, OUT = 0:

Same reasoning as above; since RESET is 0, the output will be 0.

THRES/TRIG = 0, RESET = 1, OUT = 1:

Now that RESET has been de-asserted, the SR flip-flop will function normally. For the upper comparator the inverting pin will be at a higher potential then the non-inverting pin, so “R” is held low (it won’t be asserted). The lower comparator has the opposite configuration. Its inverting pin will be at a lower potential then its non-inverting, therefore “S” is asserted. Since S is asserted, and RESET is not being held, the flip-flop sets the output to 1.

THRES/TRIG=1, RESET = 1, OUT = 0:

RESET is deserted, so the SR flip-flop won’t be locked low. For the upper comparator the inverting pin will be at a lower potential then the non-inverting pin, so “R” is held high. The lower comparator has the opposite configuration. Its inverting pin will be at a higher potential then its non-inverting, therefore “S” is low. Since S is low and R is high, the flip-flop resets the output to 0.

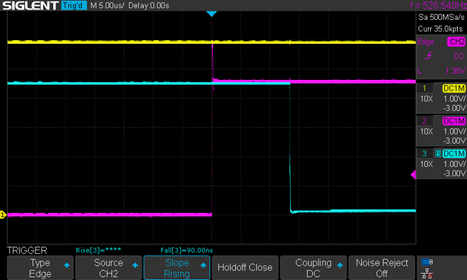

The results of the breadboarded circuit revealed an extended delay of ~15us when disabling the output via the inverting input, see below. Enabling the output via the inverting input of the AND gate took only ~100ns. However, due to the sluggish clock of this widget (~>400Hz or 2500us), the ~15us delay can be ignored.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.