This project is an open source Game Boy® compatible console Verilog RTL implementation. This project was my course project for the CMPEN 275 at Penn State back in 2017.

Original Goals for the CMPEN 275 course project

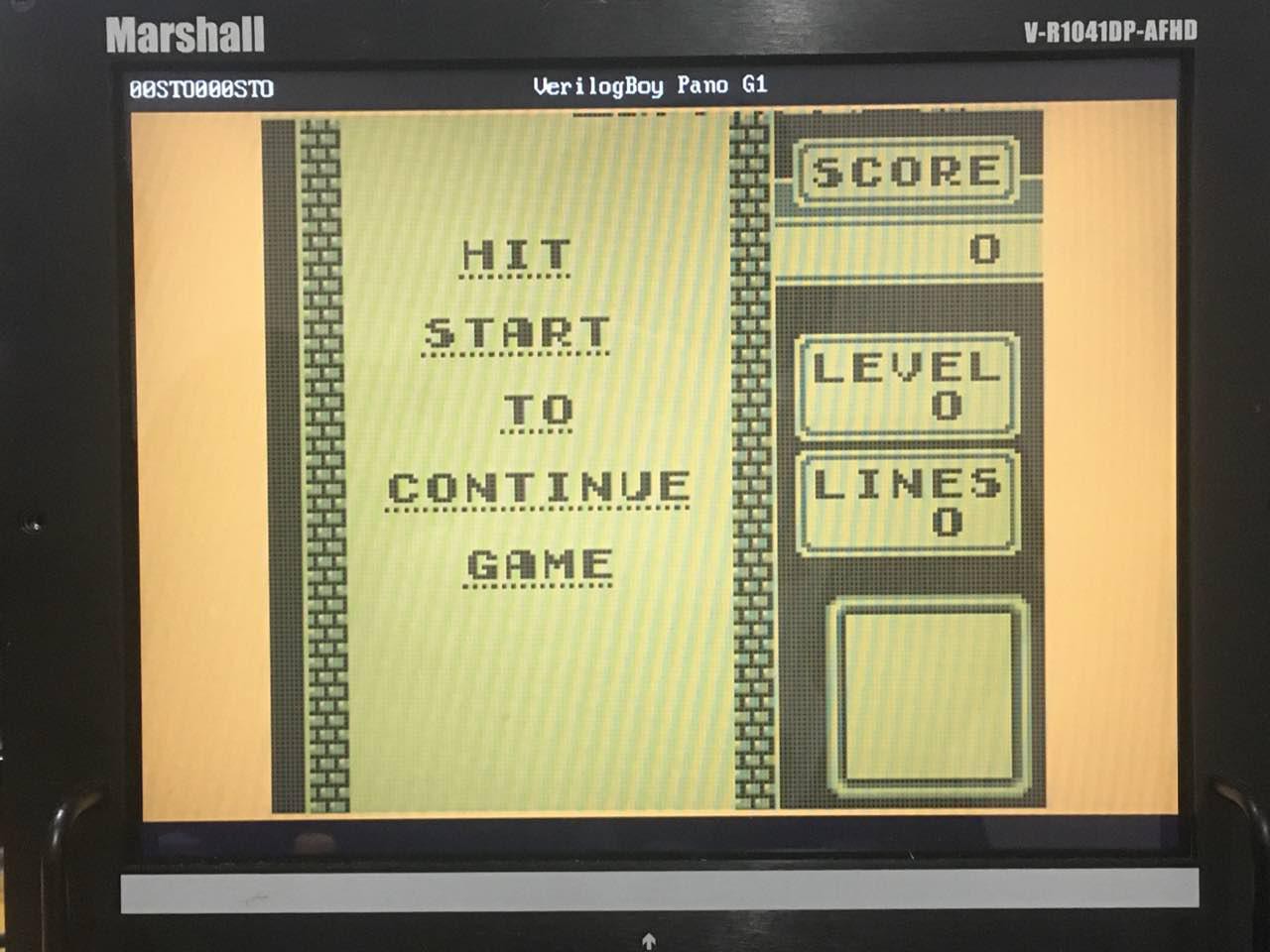

This project aims to recreate the whole Game Boy gaming system on an FPGA development board, with the ability to play commercial game like The Legend of Zelda with no major glitches.

To be specific, it should be able to run the unmodified Game Boy machine code, produce gray-scale graphics and output to an external monitor, produce the sound and output to the 3.5mm jack on the FPGA board, and accept user input to control the game. Other functionalities like serial communication and IR communication are currently not part of this project.

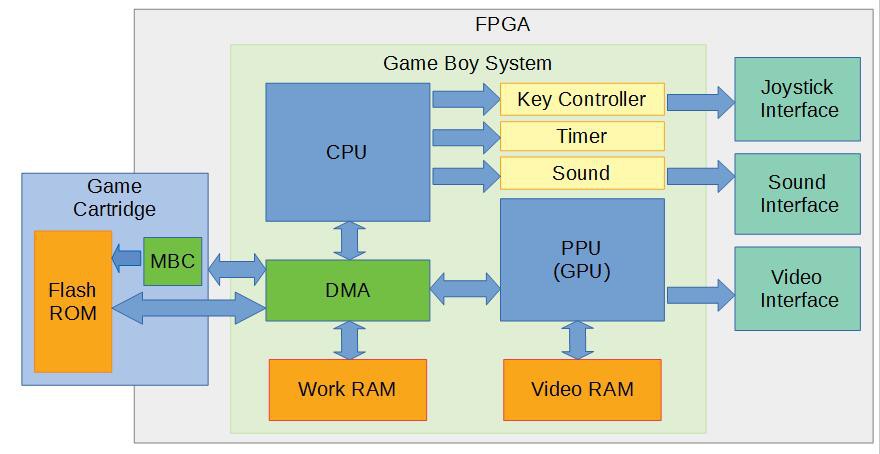

System Architecture

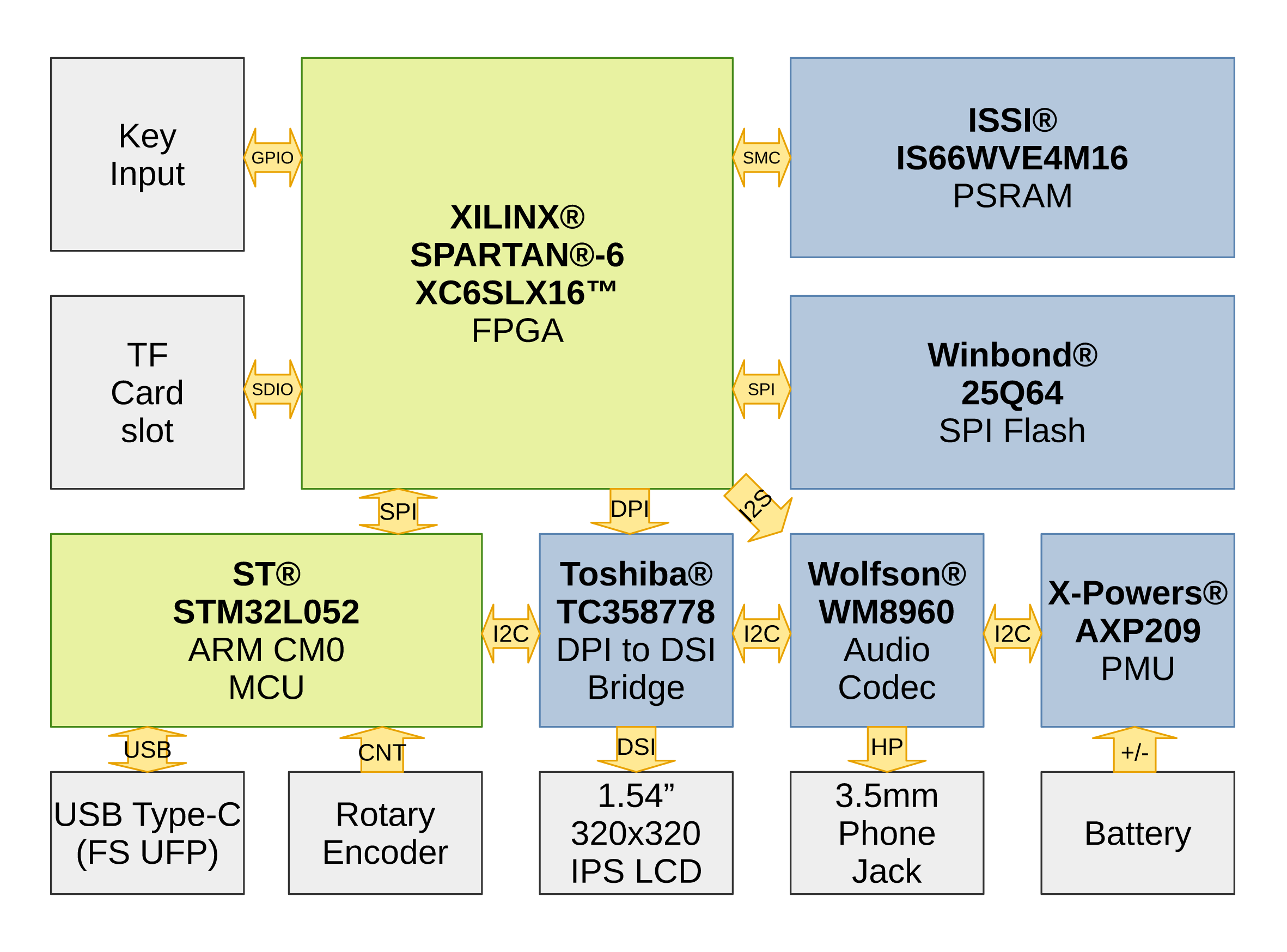

The

main system architecture is designed as follows (outdated):

There are three major parts needs to be implemented: the Game Boy CPU (8-bit CISC Processor, Intel 8080 like), the PPU (or GPU), the Sound unit. Several interfacing modules are needed to support the IO capability provided by the FPGA development board. Game ROM would be stored in on-board NOR flash, and RAM would be implemented with on-chip Block RAM.

Progress

Able to run Is That a Demo in Your Pocket with sound. See demo video! (Please turn down the volume, I found the signal from the FPGA is too hot for my recording device).

Pokemon Yellow and The Legend of Zelda: Link's Awakening DX are also tested to work with DualShock 2 support ( I should have picked a Nintendo(R) controller instead of Sony(R) one... But that's what I have. ).

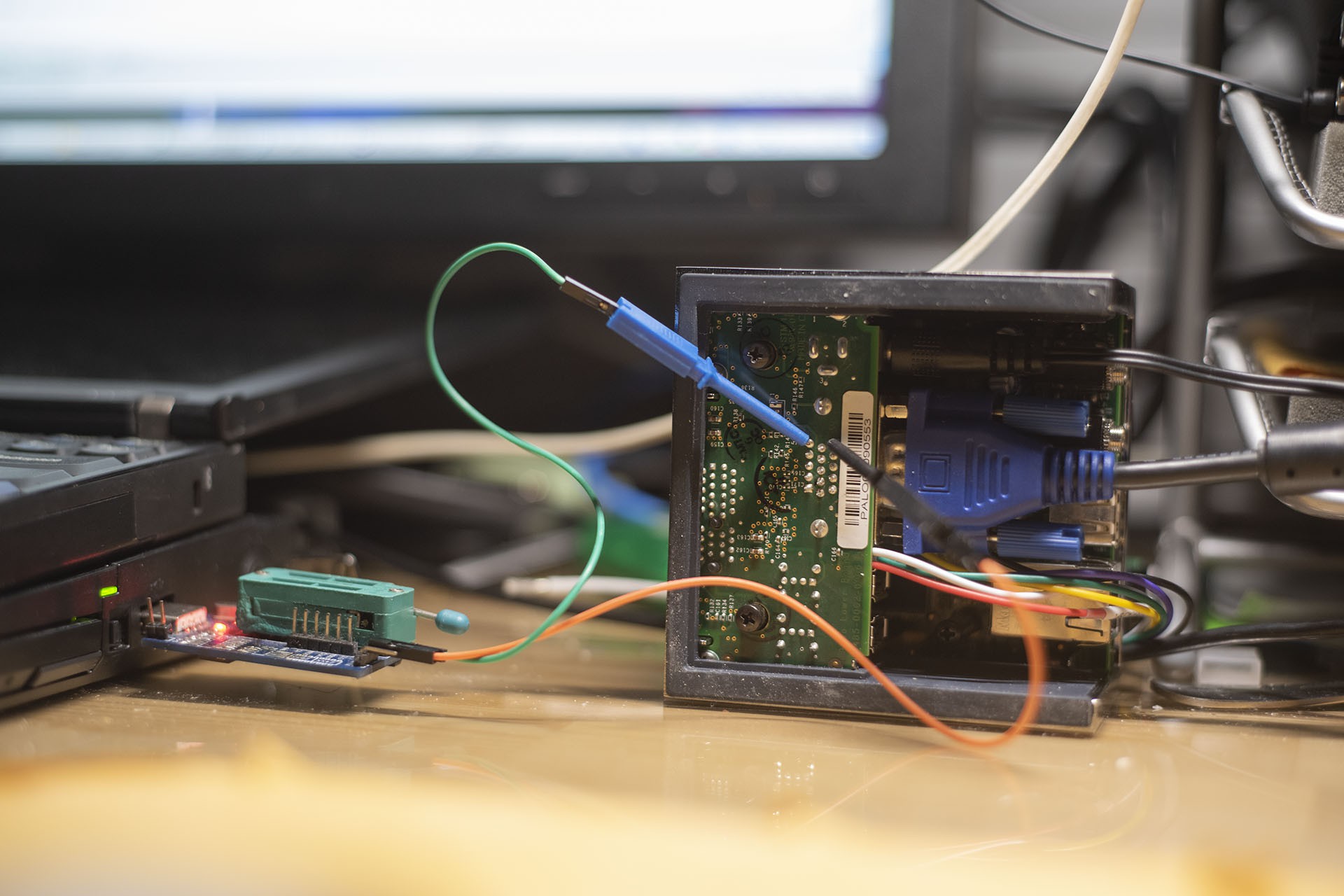

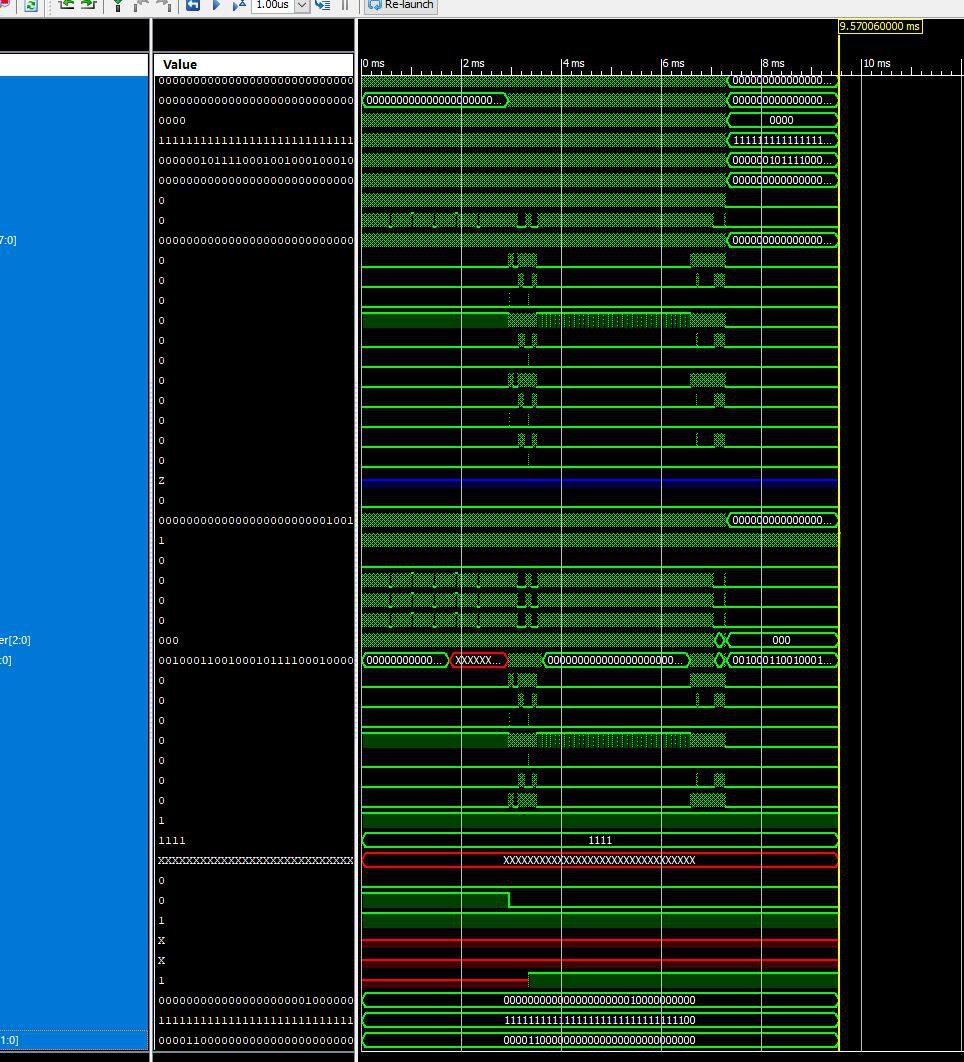

After finishing the presentation for the course project, I started refactoring the code, starting from the CPU. I have also built a verilated simulator for it so it could be easily debugged on PC.

Currently the CPU is mostly cycle accurate based on various test ROMs. However the PPU is not. It is capable of running many games already.

Wenting Zhang

Wenting Zhang I promised that there would be an update about the USB, here it is. This update would only talk about the USB 2.0 Host on the Pano Logic G1 devices with ISP1760 USB host controller, so it is probably not applicable to other platforms. The goal here is to write a set of RTL and software stack, so it is possible to use USB HID joystick/ gamepad and USB mass storage devices on the Pano G1. Speed would not be the concern here.

I promised that there would be an update about the USB, here it is. This update would only talk about the USB 2.0 Host on the Pano Logic G1 devices with ISP1760 USB host controller, so it is probably not applicable to other platforms. The goal here is to write a set of RTL and software stack, so it is possible to use USB HID joystick/ gamepad and USB mass storage devices on the Pano G1. Speed would not be the concern here.

ziggurat29

ziggurat29

Matt Stock

Matt Stock

István Hegedűs

István Hegedűs

Which CAD software you used. <a href="https://www.sassa-status.co.za/">used</a>