I'm using the WAD file from Ultimate Doom on GOG. The build process is pretty simple, but requires that you have the full GCC, binutils, and newlib tool chain, as well as the bexkat1 source. The bexkat1 source is needed only for the support library that is currently in there - there are some things that I do that are not part of newlib and so don't fit perfectly yet.

FPGA Doom

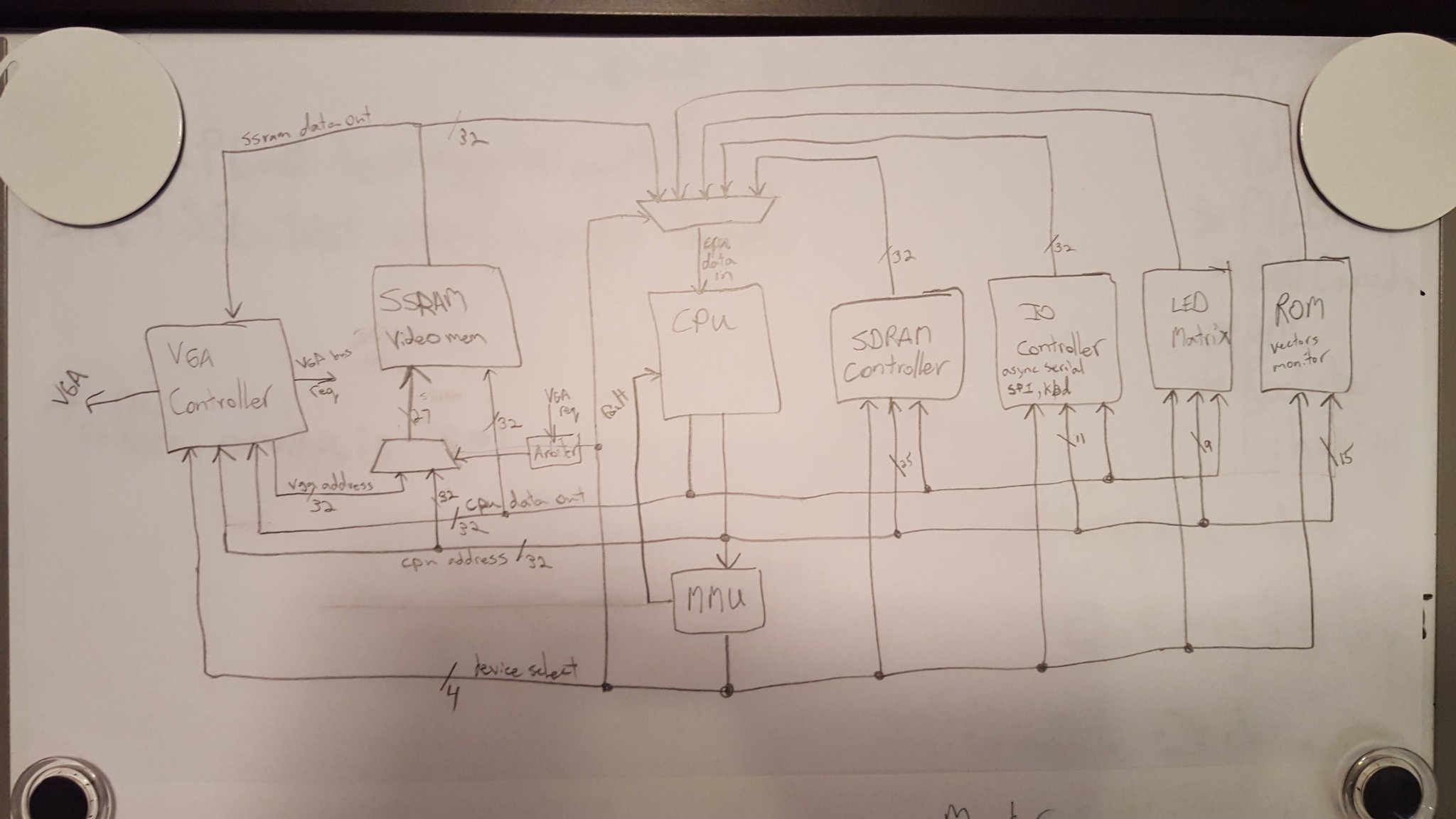

Porting the classic Doom engine to an FPGA-based system

Matt Stock

Matt Stock

Erik Piehl

Erik Piehl

Wenting Zhang

Wenting Zhang

Samuel A. Falvo II

Samuel A. Falvo II

Carson Herrington

Carson Herrington

Well it is great to have that in now a days.