Current Project Status

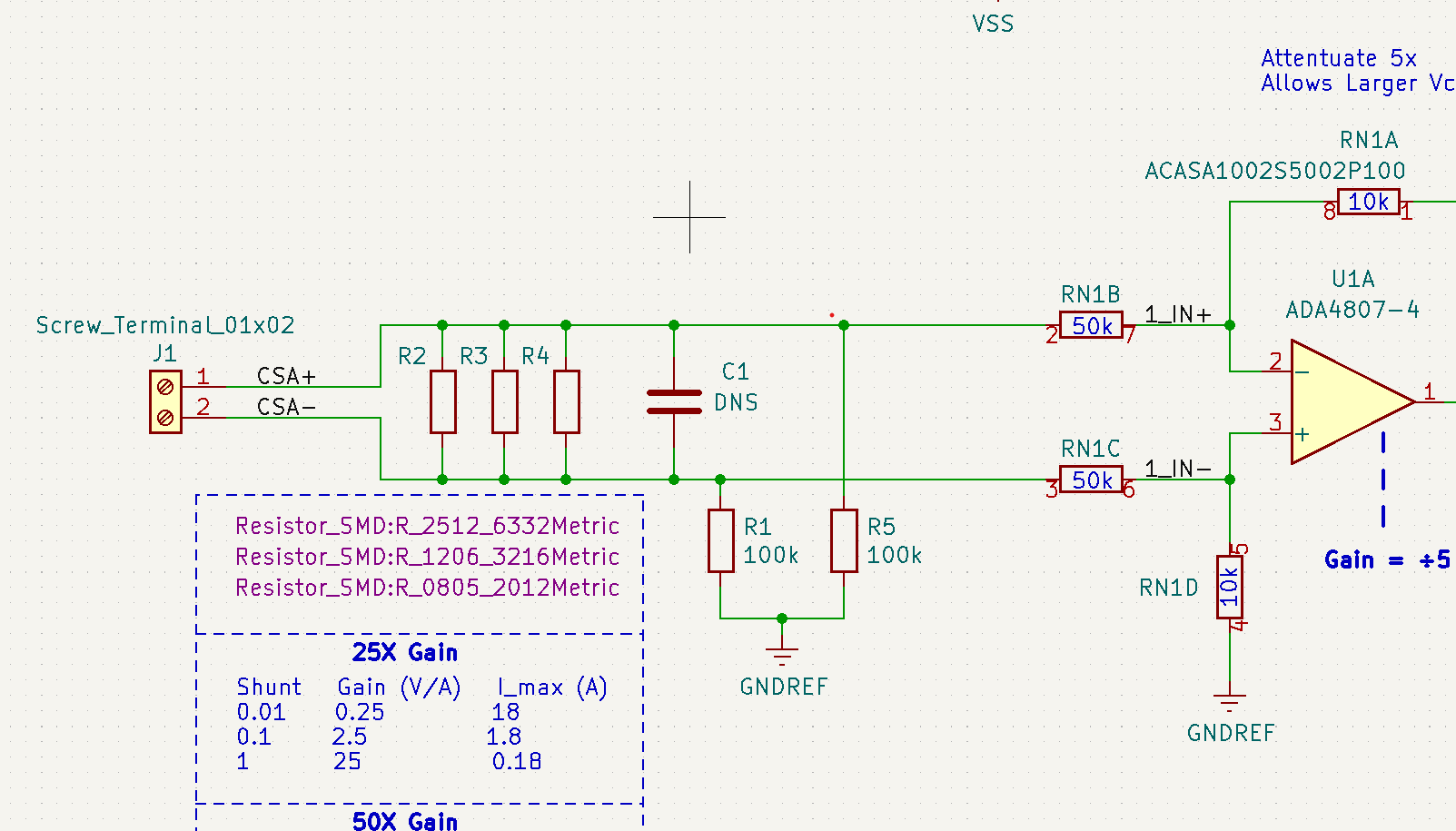

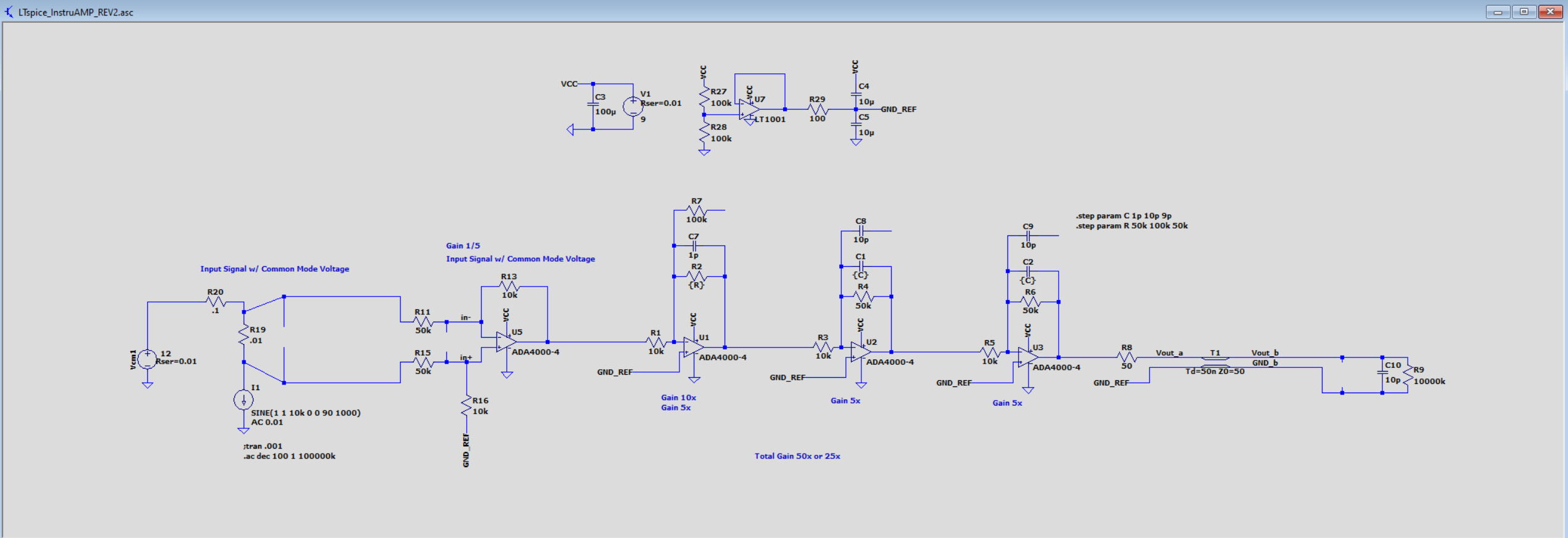

Schematic ------------------- ( ✓ )

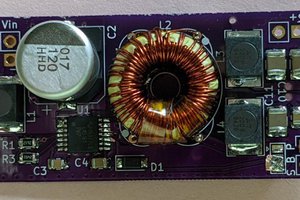

PCB Layout ----------------- ( ✓ )

Documentation ------------ ( ✓ )

Order + Assemble -------- ( ✓ )

Push 2 Hackaday --------- ( ✓ )

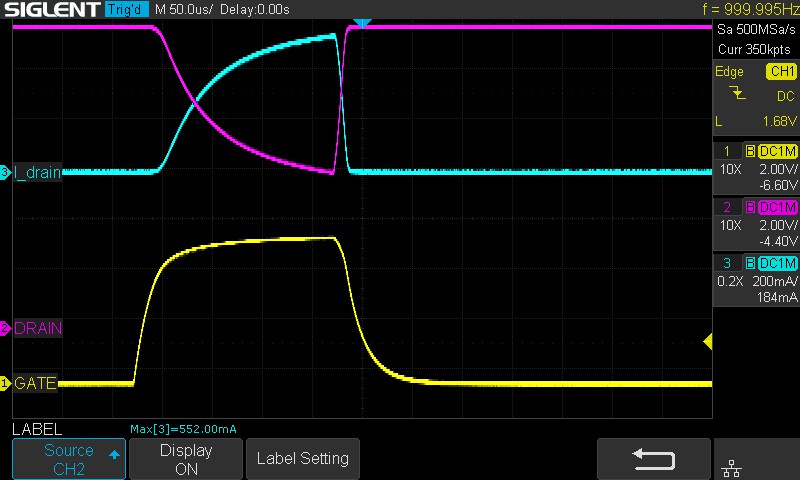

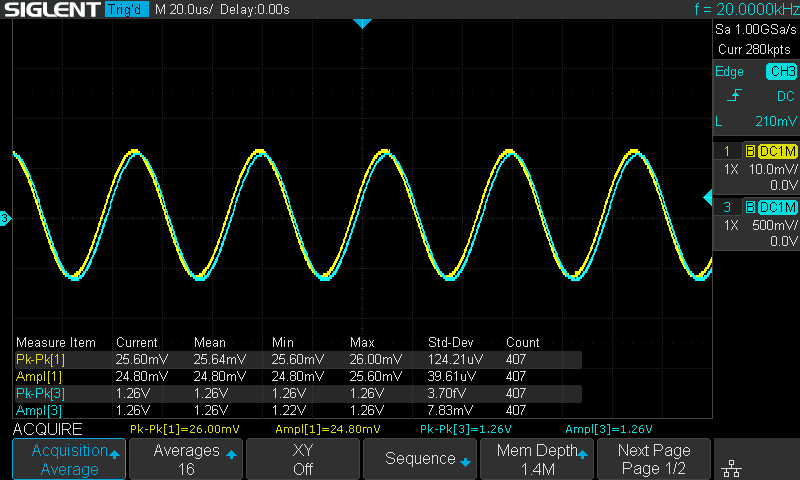

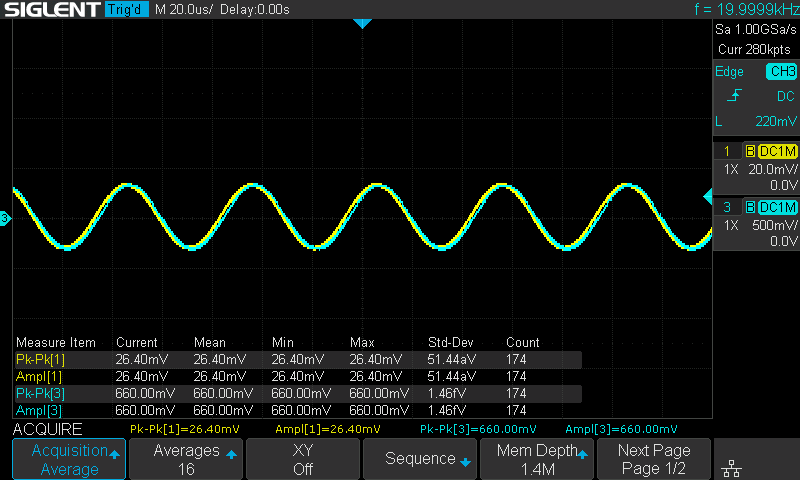

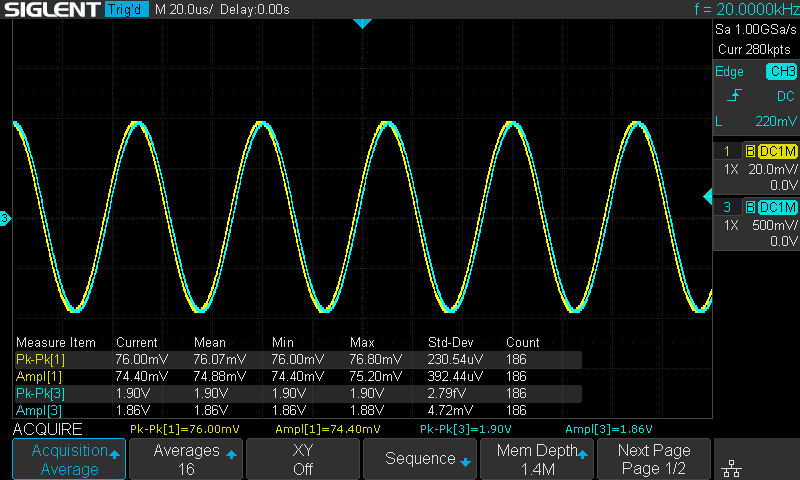

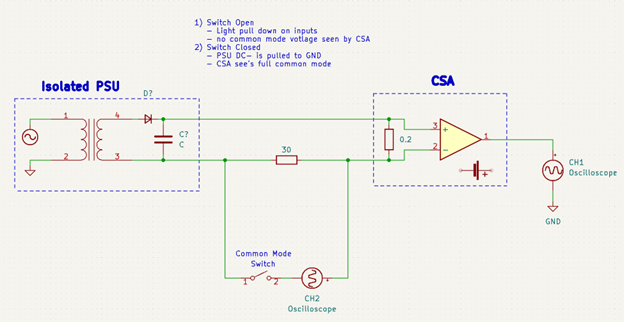

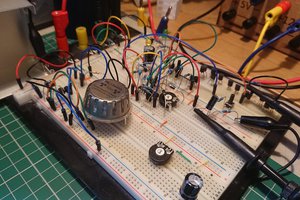

LAB: Common Mode ----- ( ✓ )

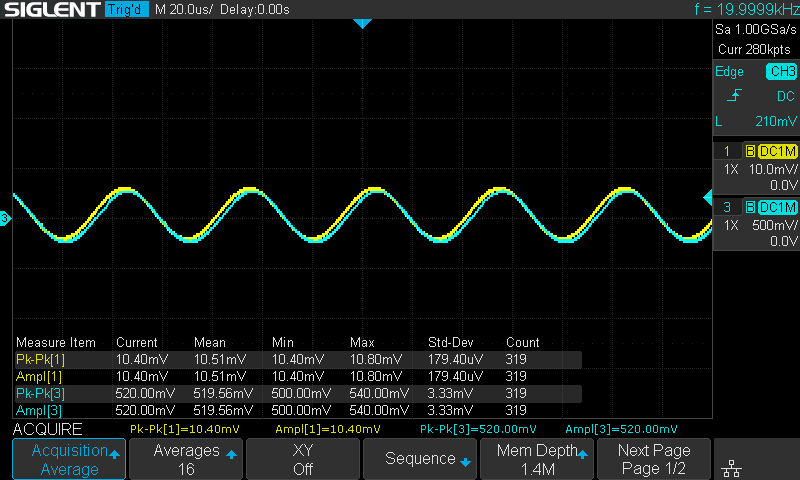

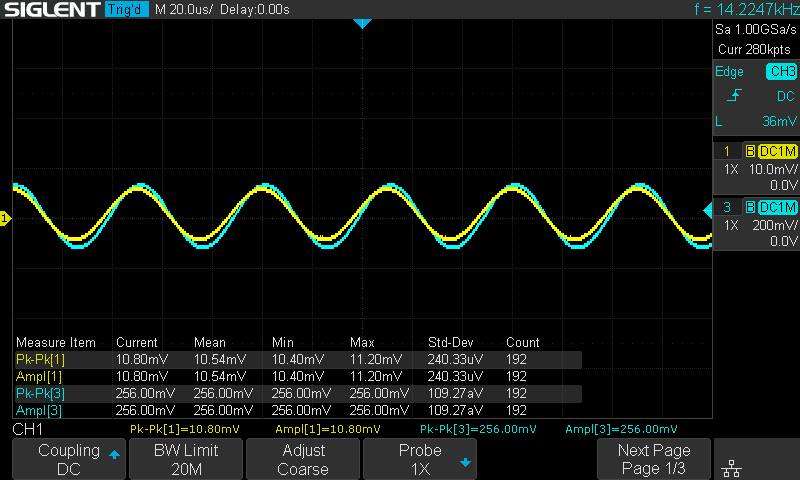

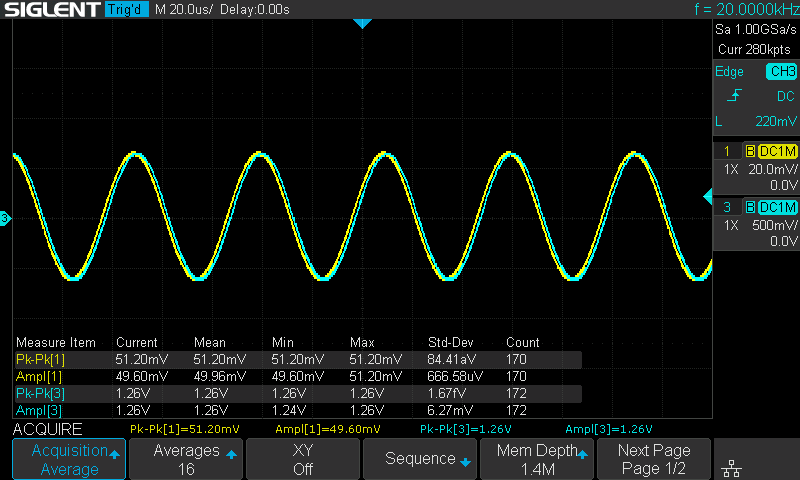

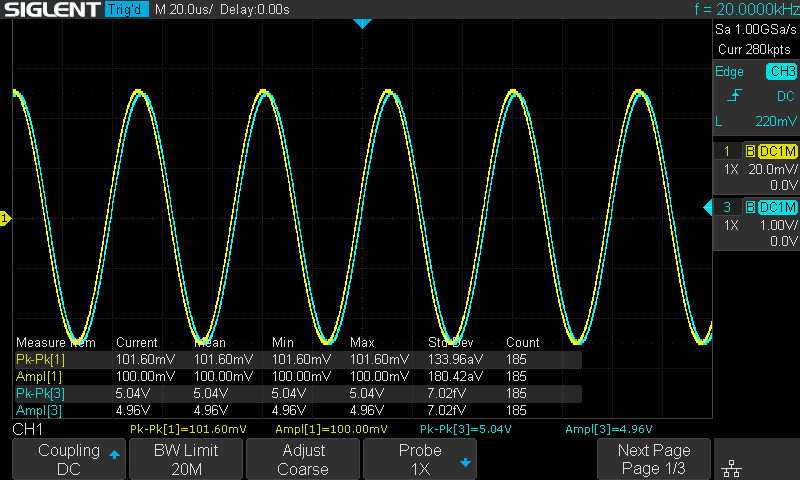

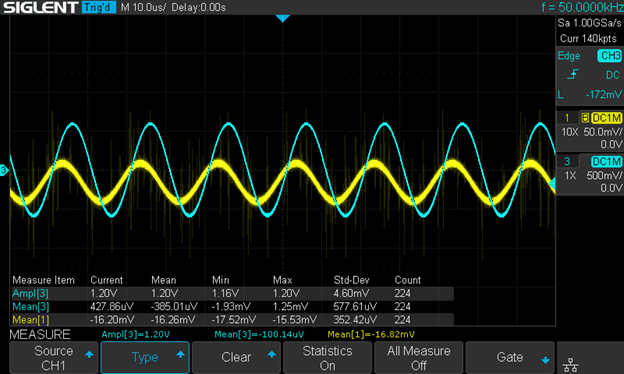

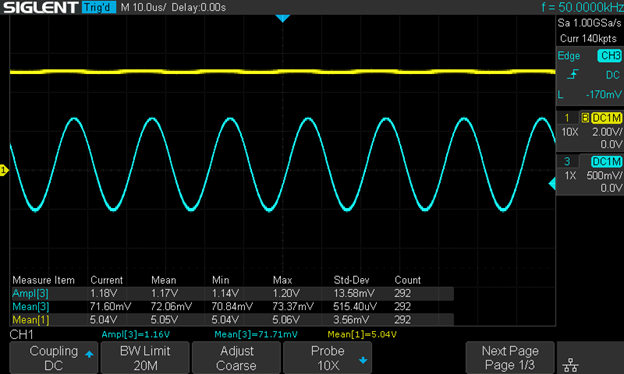

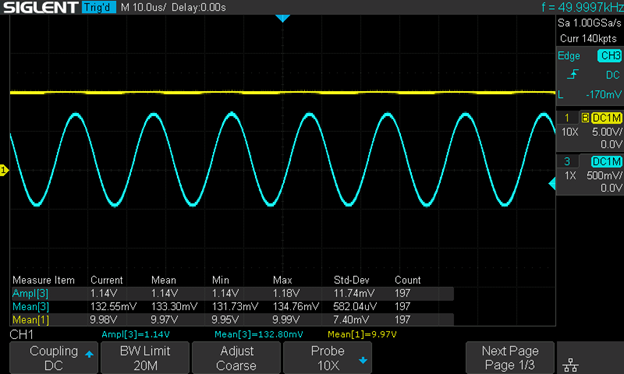

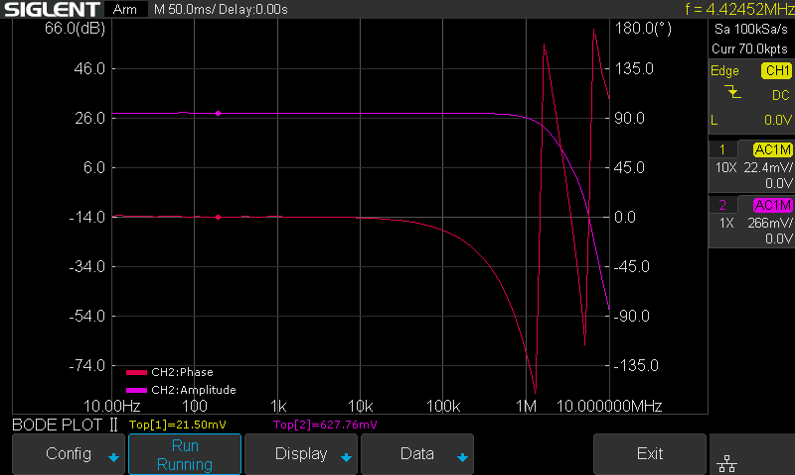

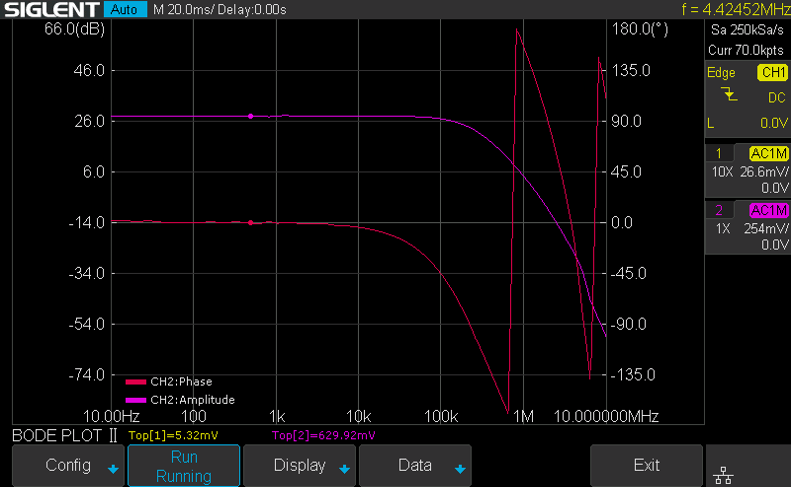

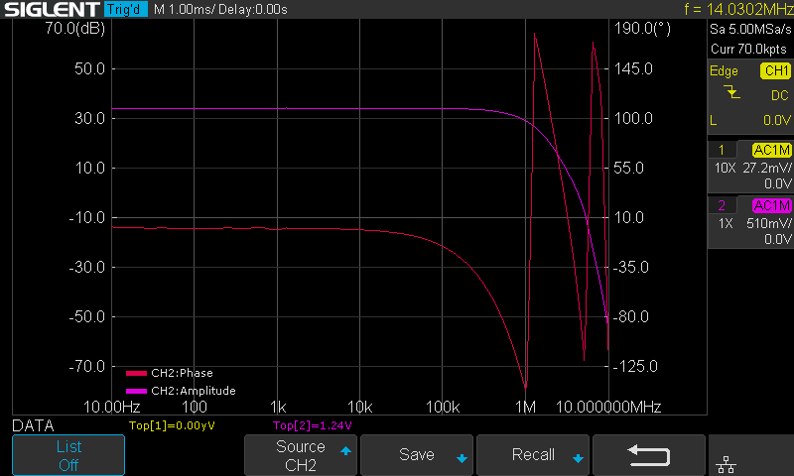

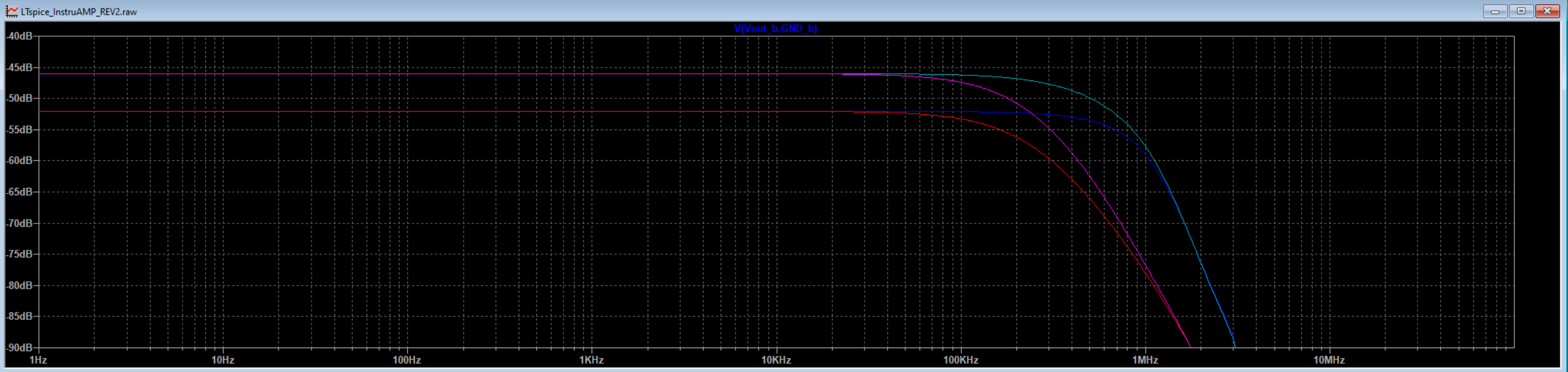

LAB: Bandwidth ------------ ( ✓ )

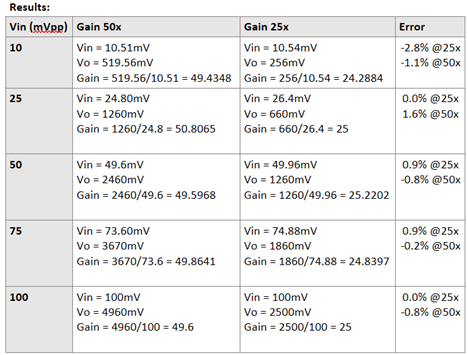

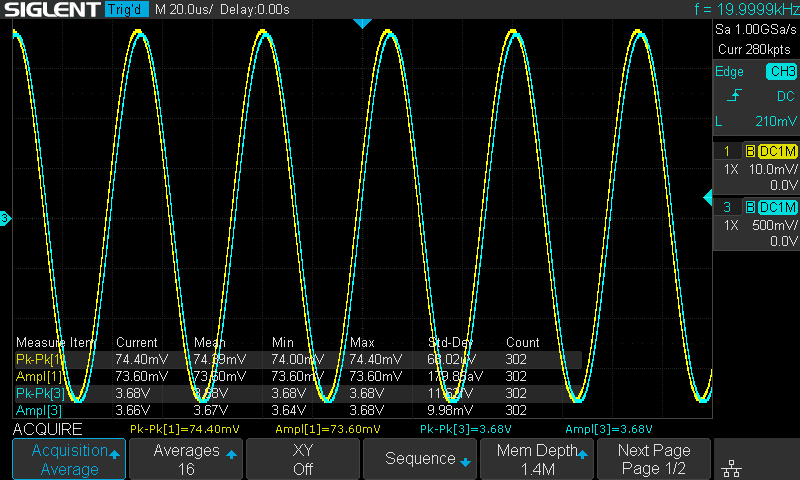

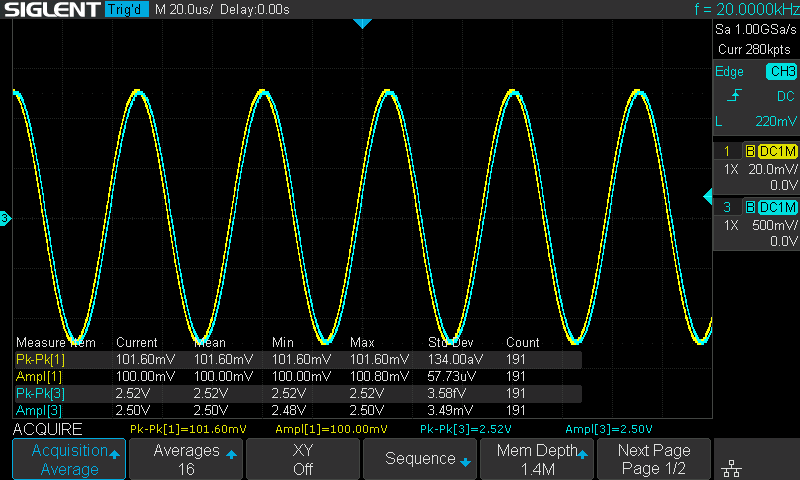

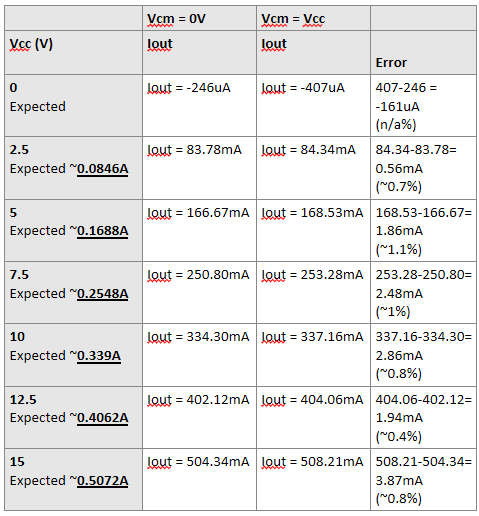

LAB: Accuracy -------------- ( ✓ )

Future Work --- Cleanup Documentation [ maybe :) ]

Lukas Koch aka Ast

Lukas Koch aka Ast

Lucy Fauth

Lucy Fauth