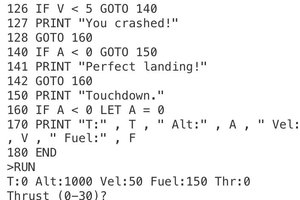

The main motivation for this project is that as a hobbyist I want to make a simple Z80 system without having to bother with programming non-volatile memory. Devising a ROMless bootstrap scheme enables this, and also reduces the amount of wiring involved. Another way of looking at it is that the boot ROM is so simple that it can be implemented with a handful of diodes and resistors rather than an IC.

This scheme could also be useful in systems that include a Z80 alongside another processor - the other processor could provide a four-wire output that could be used to bootstrap the Z80, removing the need to have a ROM for the Z80.

It could also be used as an in-circuit programming method to program the flash memory in a Z80 system that has RAM and flash memory. This would require a switch that makes RAM map to the whole address space during bootstrapping, the lower part during flash programming, and the upper part during normal operation.

will.stevens

will.stevens

agp.cooper

agp.cooper

Bruce Land

Bruce Land

A long time ago, bootloading of a Z80 using clock, reset and nmi was developed: http://www.z80.info/jmz8boot.htm

I think you can get inspiration from that!