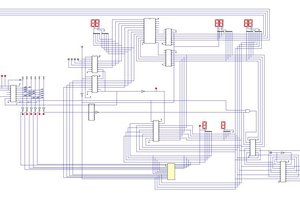

ARISC is based at modified Harvard architecture what means instruction data(ROM)and program data(RAM) are separated but this areas of memory sharing magistrals. The μP is based on RISC architecture which mean control unit use less LUT’s and we can’t compute on data stored in random access memory. If we need to use this data we need use assembly instruction LOAD for copy value to general purpose register later compute and use instruction STORE to copy value from general purpose register to RAM.

μP features:

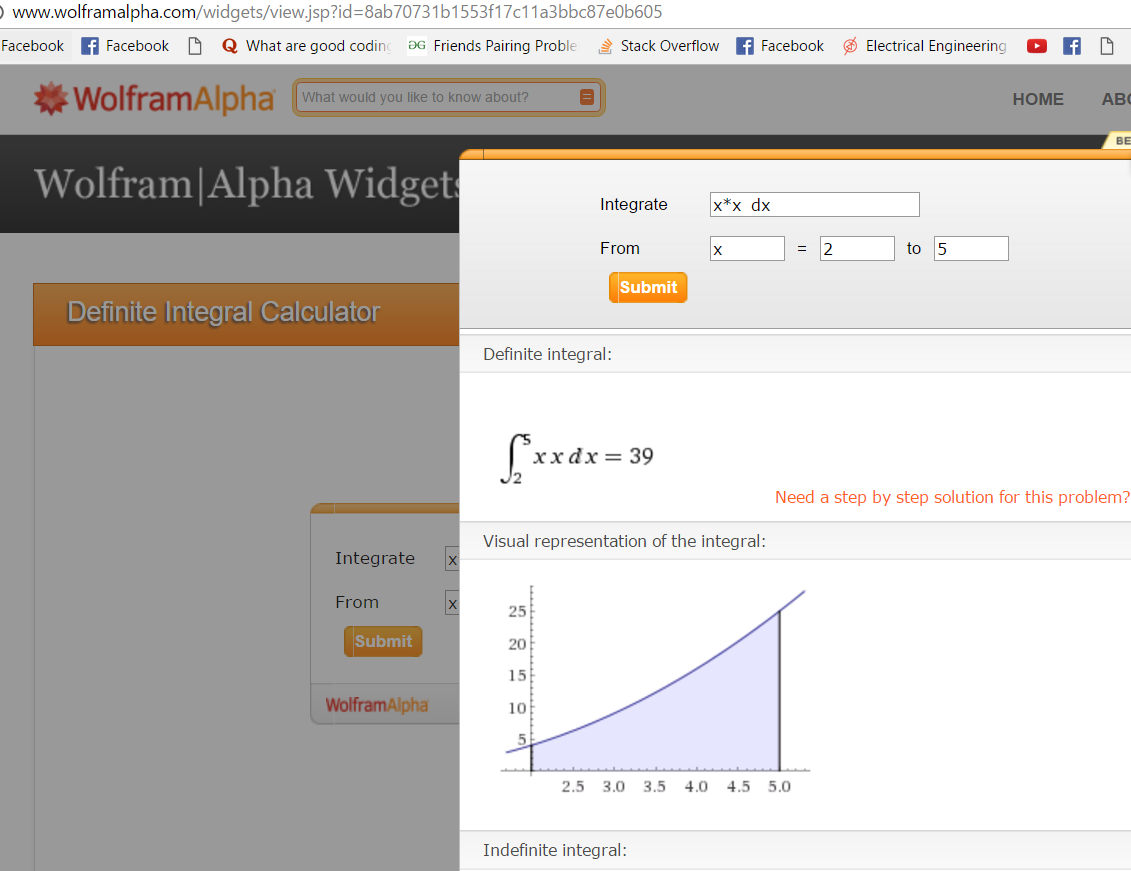

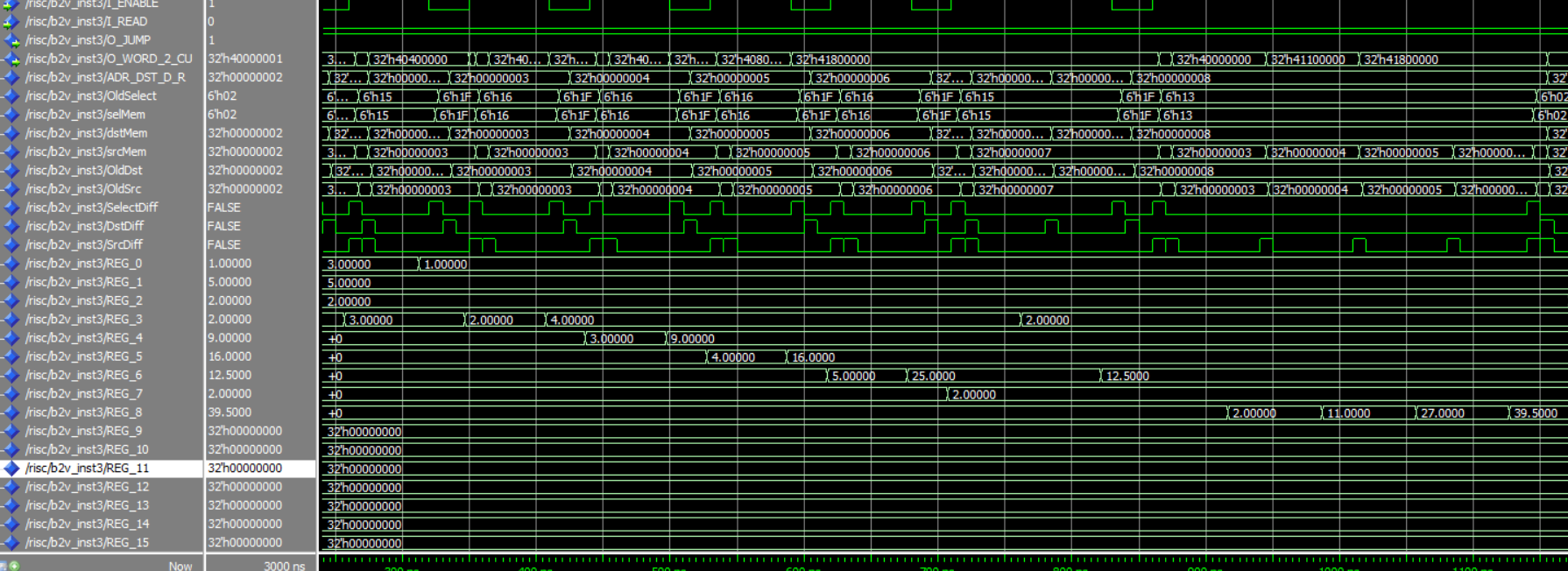

Floating Point Unit – (add, sub, mul, div, cmp’s) hardware instructions

16 general purpose registers

Clock speed 20MHz at Altera Cyclone IV E: EP4CE115F29C7

Functional Programing

Turing completeness

Stack (16 addresses)

Assembly language – our assembly consist about 40 instructions basic AL for int32(U2) and float IEEE754. The language consist branch instructions like (comparations, jumps, calls, type conversion)

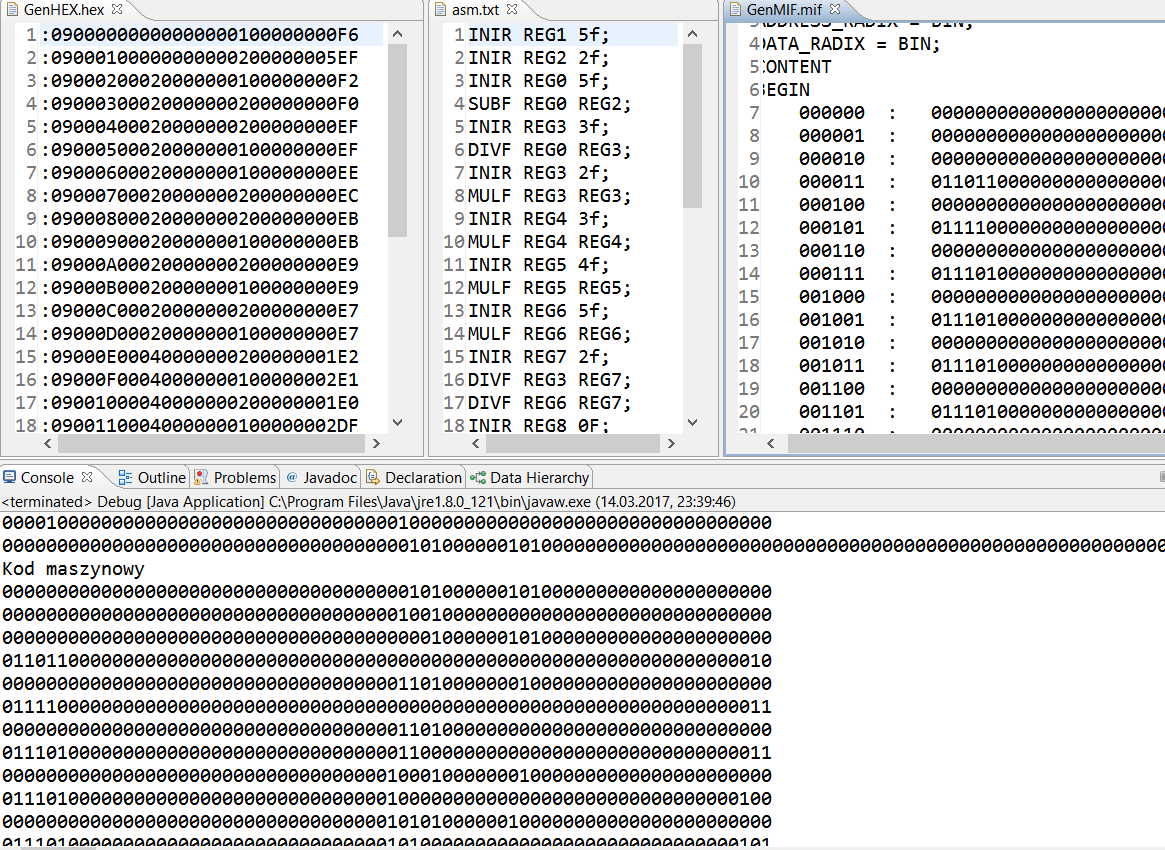

Compiler – written in Java transforms assembly language to machine code. Compiler is integrated with Memory Initialization File (.mif) and Hexadecimal (Intel-Format) File (.hex).

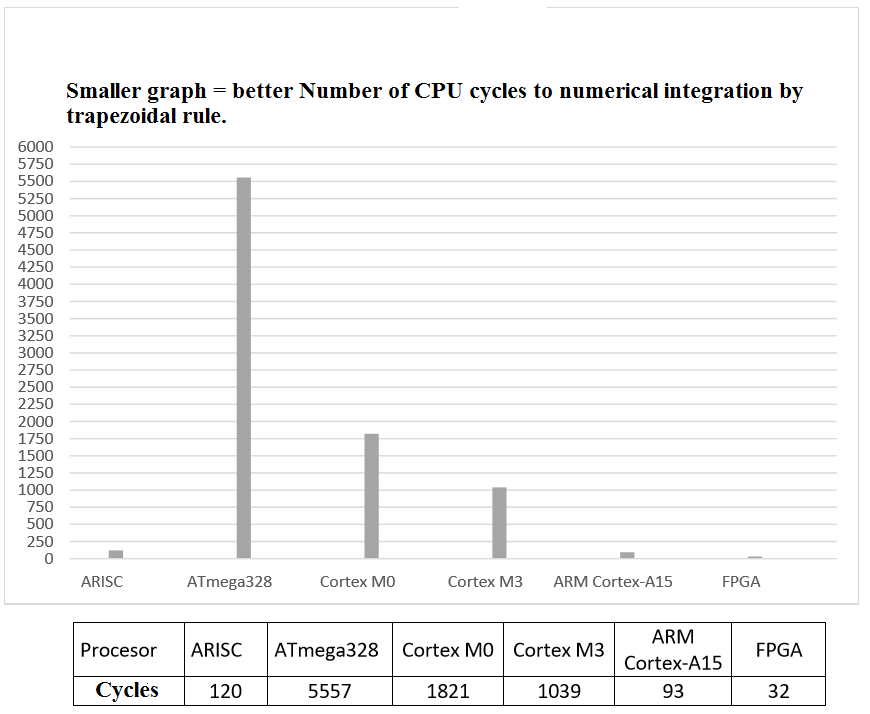

Architecture performance - is similar to Cortex A15 for Numerical Integration by trapezoidal. To compare others μP and μC w our design we used IAR workbench studio (kickster edition) and ModelSim.

Szoftveres

Szoftveres

ammarbhayat28

ammarbhayat28

I totally agree with Yann on what he says. I'm tired of reading theses that don't give their source code so I can verify their claims. Where is the truth? And what is the point if it is not for knowledge sharing? I read a few that looked interesting but many gave nothing to back up their claims. Those theses are really all nonsense in the end.